USB 2.0 Tuning Guide

PRELIMINARY INFORMATION

Jetson AGX Orin Series Tuning and Compliance Guide DA-11040-001_v0.7 | 3

4. Set RS (Run/Stop) bit in the T_XUSB_XHCI_OP_USBCMD_0[0] = 0.

0x03610020: T_XUSB_XHCI_OP_USBCMD_0

5. Wait for the HCHalted (HCH) bit in the T_XUSB_XHCI_OP_USBSTS_0[0] = 1.

0x03610024: T_XUSB_XHCI_OP_USBSTS_0

6. Set the xUSB Port Test Control registers in PORTPMSCHS register. See “Host Mode

Testing Registers” section.

Note: Per USB 2.0 specification, only a single downstream facing port can be in test_mode at a

given time.

7. Disable Pad PD (power down) by clearing the

T_XUSB_PADCTL_USB2_OTG_PADx_CTL_0_0[26] = 0.

Port 0: 0x03520088: T_XUSB_PADCTL_USB2_OTG_PAD0_CTL_0_0

Port 1: 0x035200C8: T_XUSB_PADCTL_USB2_OTG_PAD1_CTL_0_0

Port 2: 0x03520108: T_XUSB_PADCTL_USB2_OTG_PAD2_CTL_0_0

Port 3: 0x03520148: T_XUSB_PADCTL_USB2_OTG_PAD3_CTL_0_0

8. Plug in the test fixture to start the USB 2.0 eye diagram test.

USB 2.0 Eye Diagram Registers

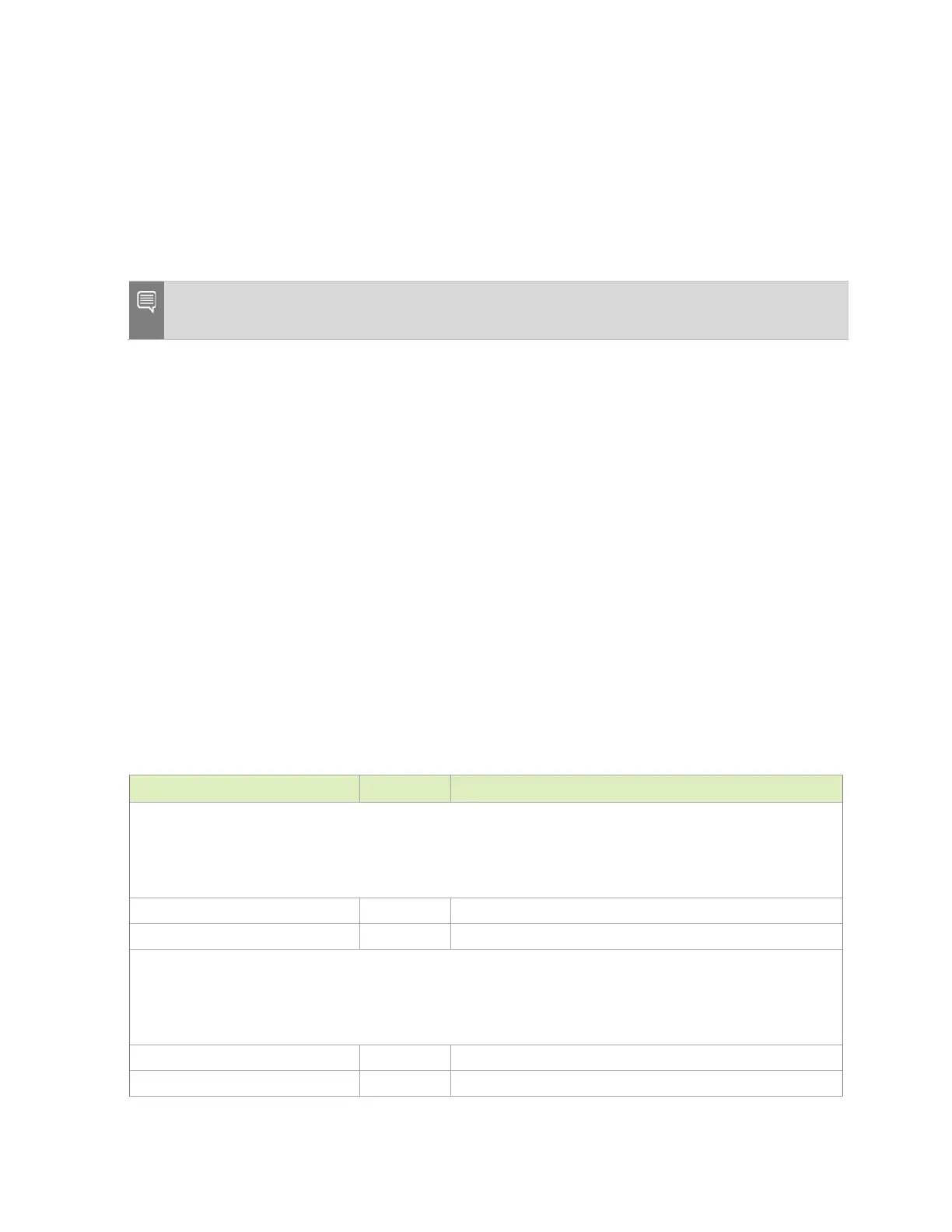

Table 2 lists the NVIDIA Orin

™

USB registers that are needed to tune the USB 2.0 eye diagram.

See “Tuning Procedure and Registers” section on how to use these registers during

characterization.

Table 2. NVIDIA Orin USB Registers

Register Name Bit Field Description

XUSB_PADCTL_USB2_OTG_PAD0_CTL_0_0 (Address 0x03520088) for Port 0

XUSB_PADCTL_USB2_OTG_PAD1_CTL_0_0 (Address 0x035200C8) for Port 1

XUSB_PADCTL_USB2_OTG_PAD2_CTL_0_0 (Address 0x03520108) for Port 2

XUSB_PADCTL_USB2_OTG_PAD3_CTL_0_0 (Address 0x03520148) for Port 3

HS_SLEW (See Note 1) 8:6 HSSLEW (high-speed slew rate control)

HS_CURR_LEVEL (See Note 2) 5:0 Setup (high-speed drive strength control)

XUSB_PADCTL_USB2_OTG_PAD0_CTL_1_0 (Address 0x0352008C) for Port 0

XUSB_PADCTL_USB2_OTG_PAD1_CTL_1_0 (Address 0x035200CC) for Port 1

XUSB_PADCTL_USB2_OTG_PAD2_CTL_1_0 (Address 0x0352010C) for Port 2

XUSB_PADCTL_USB2_OTG_PAD3_CTL_1_0 (Address 0x0352014C) for Port 3

RPD_CTRL 30:26 RPD_CTRL (15K host pull-down)

TERM_RANGE_ADJ 6:3 ATERM (high-speed termination control)

Loading...

Loading...