36

Basic Concepts Section 2-1

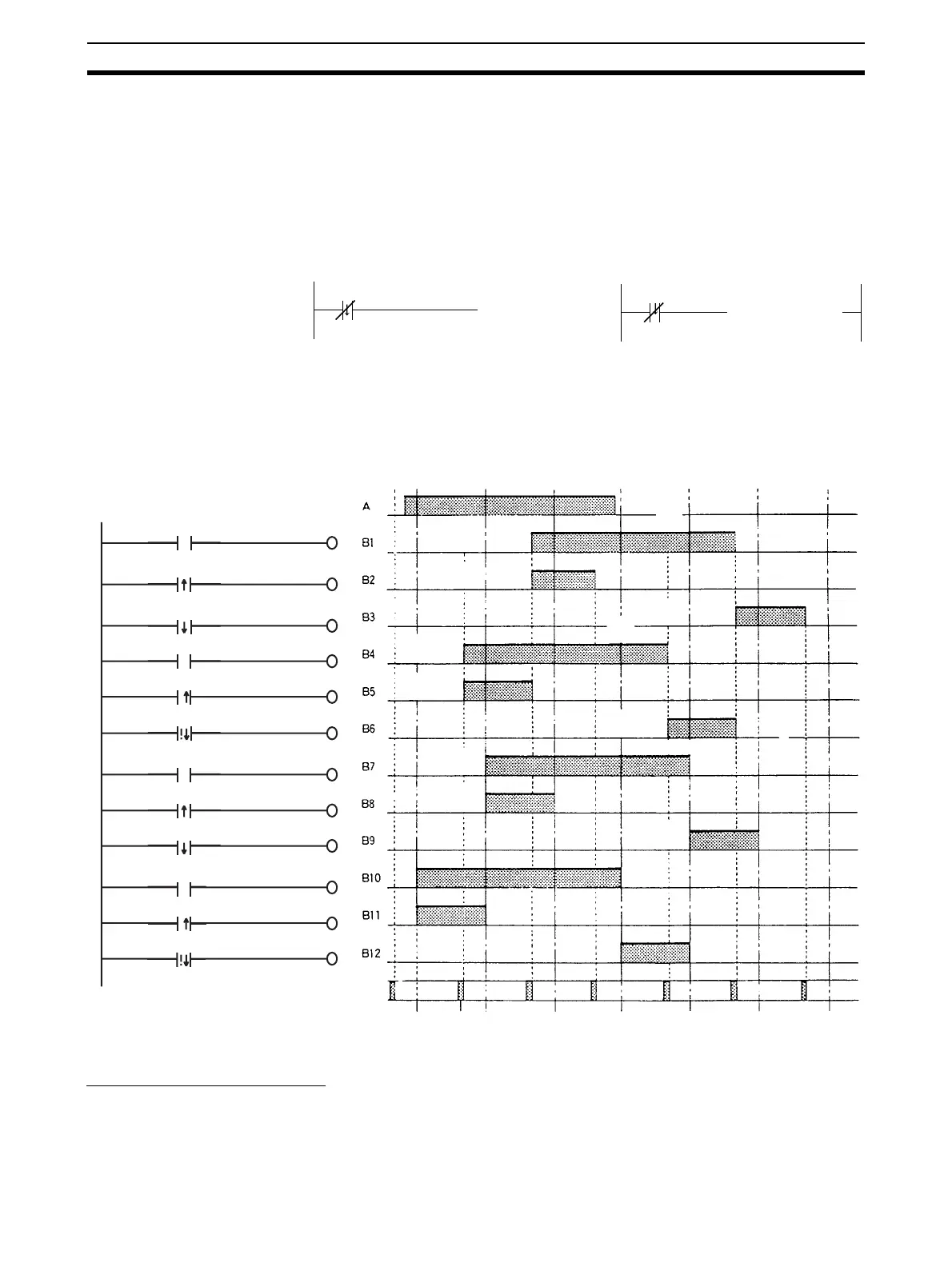

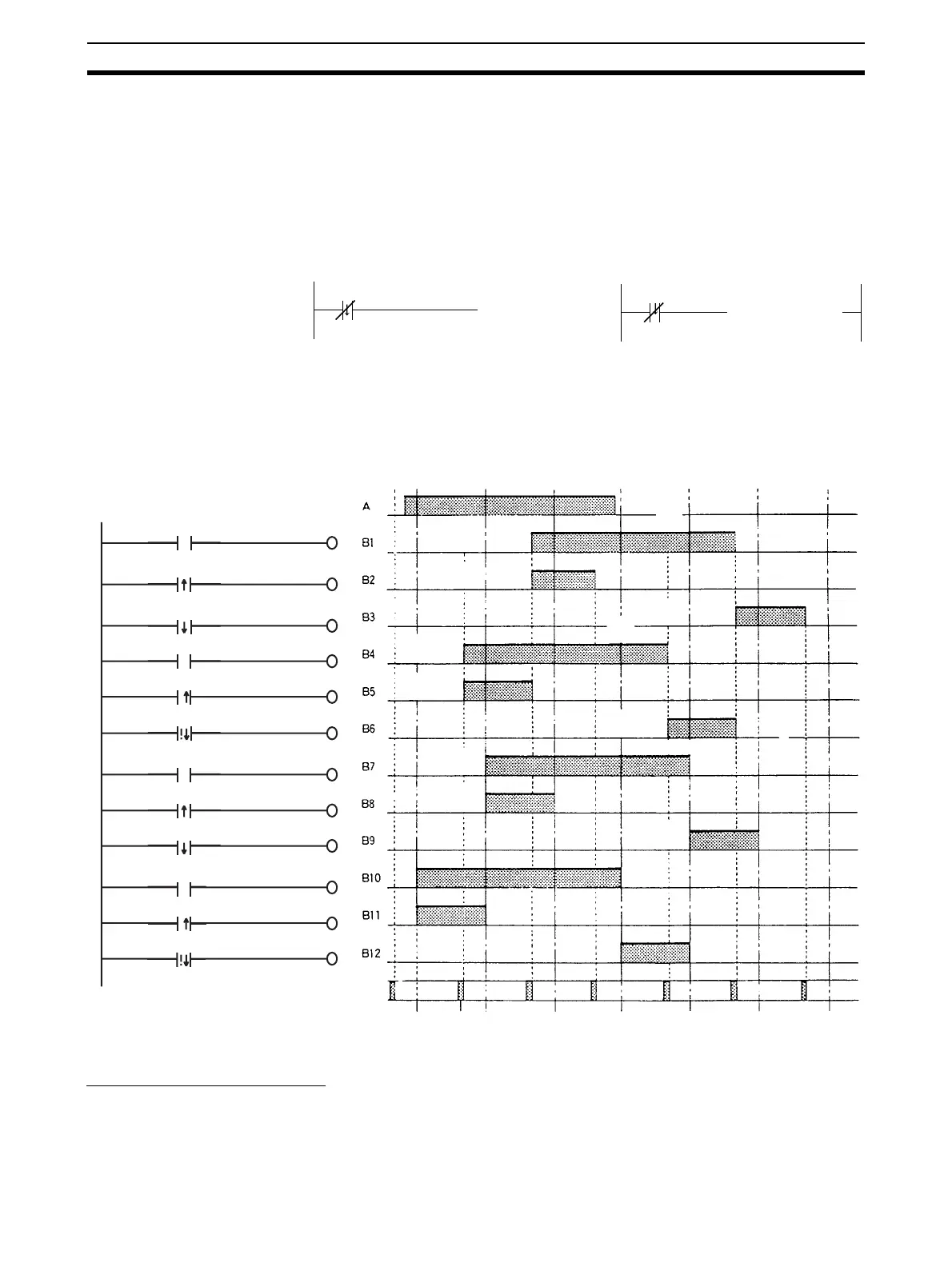

FERENTIATE DOWN (DIFD) instructions, power flow

differentiation UP and DOWN instructions as well as upwardly/

downwardly differentiated LOAD instructions (@LD/%LD).

• Input Instructions (Logical Starts and Intermediate Instructions): The

instruction reads bit status, makes comparisons, tests bits, or perform

other types of processing every cycle and will output an OFF execution

condition (power flow stops) when results switch from ON to OFF. The

execution condition will turn ON the next cycle.

2-1-9 I/O Instruction Timing

The following timing chart shows different operating timing for individual

instructions using a program comprised of only LD and OUT instructions.

Differentiated Instructions

• A differentiated instruction has an internal flag that tells whether the previ-

ous value is ON or OFF. At the start of operation, the previous value flags

for upwardly differentiated instruction (DIFU and @ instructions) are set to

ON and the previous value flags for downwardly differentiated instructions

Downwardly differentiated input instruction

Example

OFF execution condition created for one

cycle only when CIO 00103 goes from

ON to OFF.

0001

03

Input

read

CPU pro-

cessing

Instruction

executed.

I/O refresh

Input

read

Input

read

Input

read

Input

read

Input

read

Input

read

Input

read

Input

read

Input

read

Input read

Input

read

A

A

A

A

A

A

A

A

A

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

A

A

B11

B12

!

!

!

!

A

!

!

!

!

!

!

Loading...

Loading...