Circuit Descriptions

EN 46 Q548.1E LA7.

2009-Apr-03

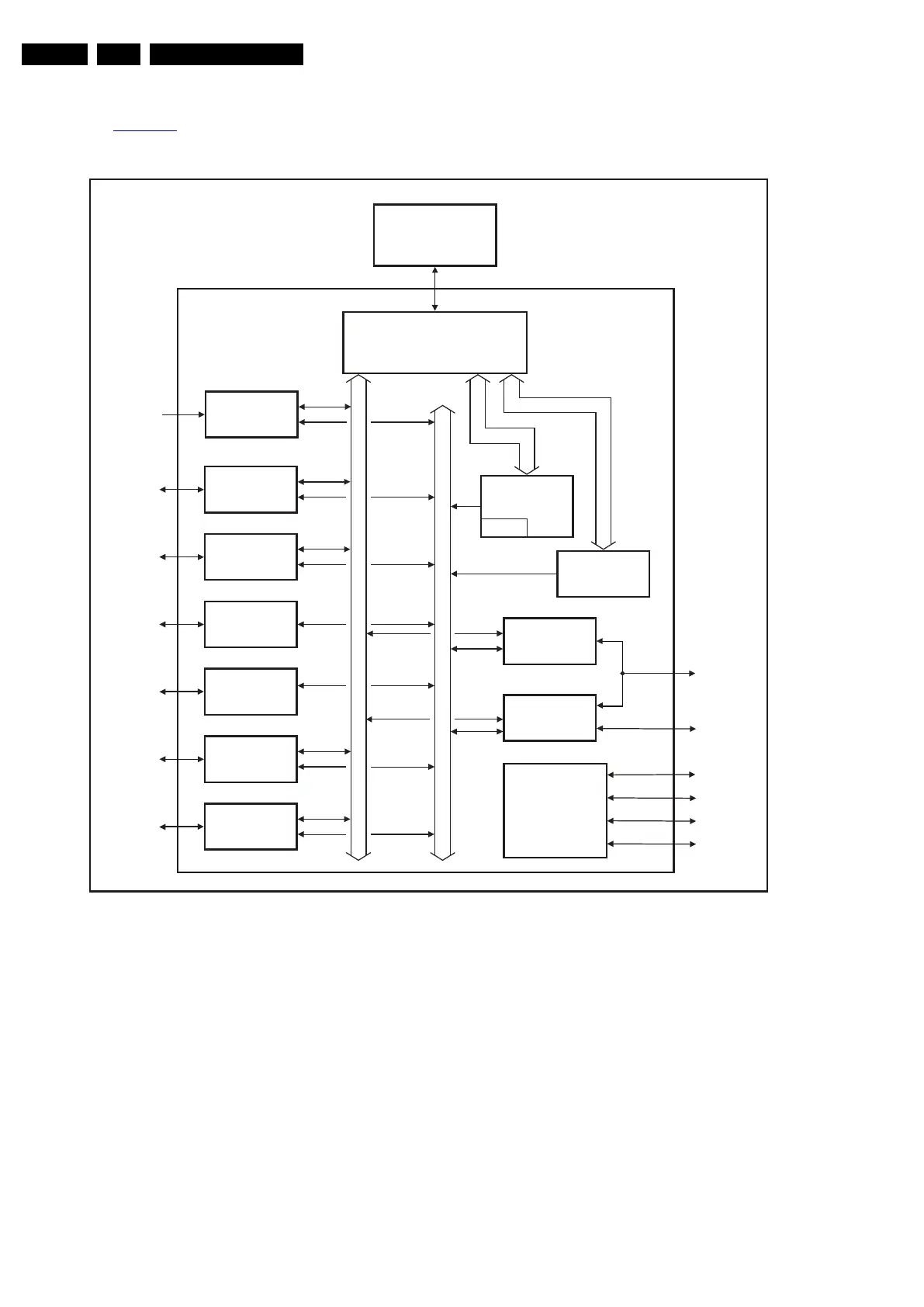

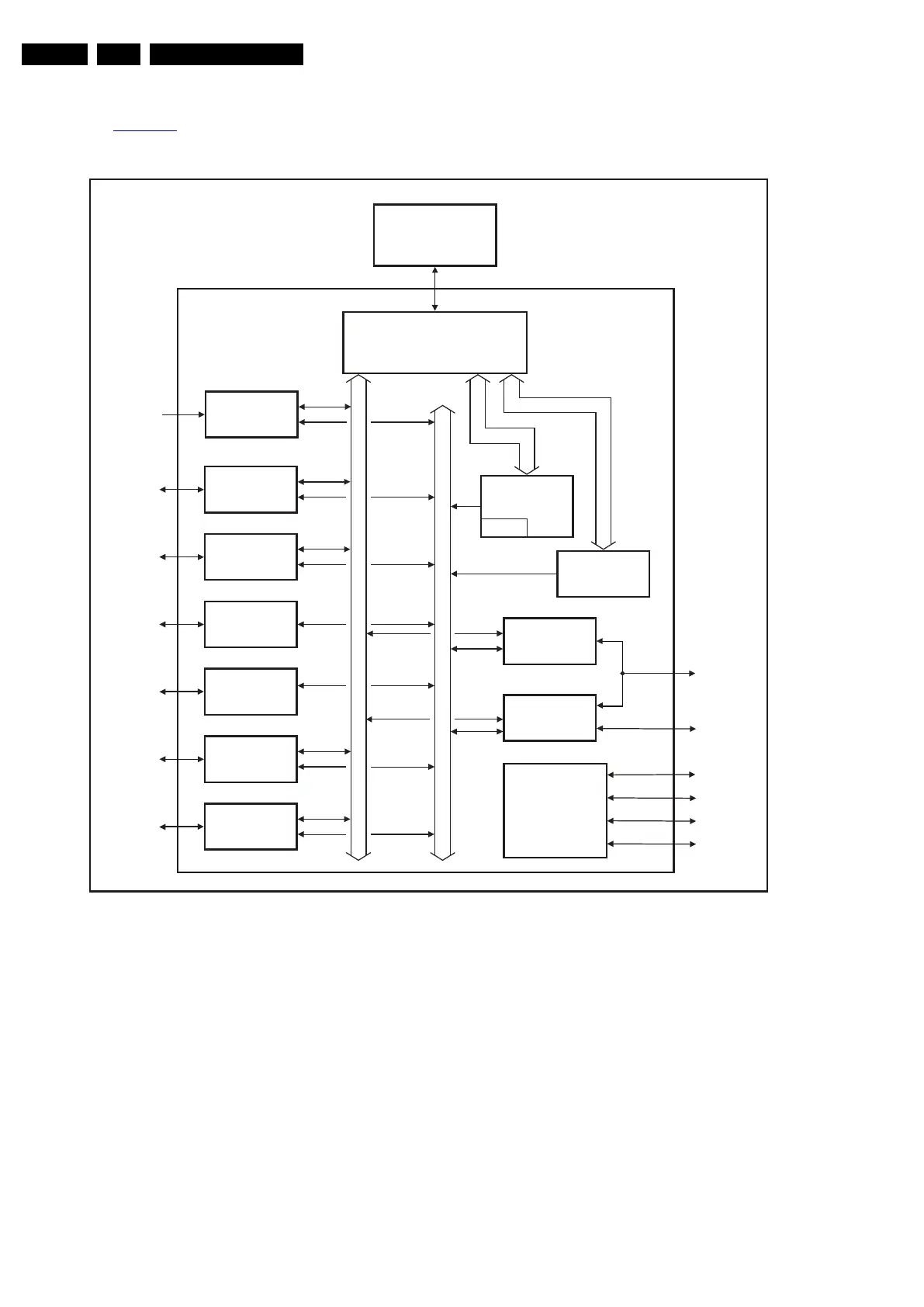

7.6.3 Connectivity and Compute Subsystem

Refer to Figure 7-12

for the connectivity and compute

subsystem.

Figure 7-12 PNX8543 connectivity and compute subsystem

The Connectivity Subsystem consists of:

• PCI/XIO interface

• USB2.0 interface

• Three 2-wire UARTs

• Four Master/Slave I

2

C interfaces

• Common Interface/Conditional Access Interface.

The Computing Subsystem consists of:

• 32-bit MIPS RISC core

• Enhanced JTAG (EJTAG) block inside the MIPS

• JTAG_MMIO blocks

• TV controller

• Audio/Video DSP (AV_DSP)

• Memory Control Unit (MCU).

7.6.4 Service Notice - FLASH RAM / PNX8543 exchange

The FLASH RAM (item 7M00) and/or PNX8543 (item 7600)

can only be exchanged by an authorised central workshop with

dedicated programming tools. Due to the presence of (CI+)

keys in the components, unauthorised exchange of these

components will always result in a defective board.

7.7 Common Interface CI+

Together with this platform, an extension to the Common

Interface (CI) Conditional Access system is added, called CI+.

CI+ or Common Interface Plus is a specification that extends

the Common Interface (DVB-CI) as described in the digital

broadcasting standard DVB.

18440_205_090226.eps

090226

JTAG_MMIO

UART2

UART1

IIC2_DMA

IIC3_DMA

MIPS

4KEc

SYSTEM

CONTROLLER

80C51

PCI_XIO

CAI

MCU_DDR

DMA BUS

DCS-NETWORK

DDR2-SDRAM

I2C-2

I2C-3

EJTAG

PNX8543x

UART-1

UART-2

I2C-MC

UART-3

PWMs

GPIOs

CI/CA

PCI/XIO

EJTAG

USB2.0USB

AVDSP

IIC4_DMA

I2C-1

Loading...

Loading...