2828

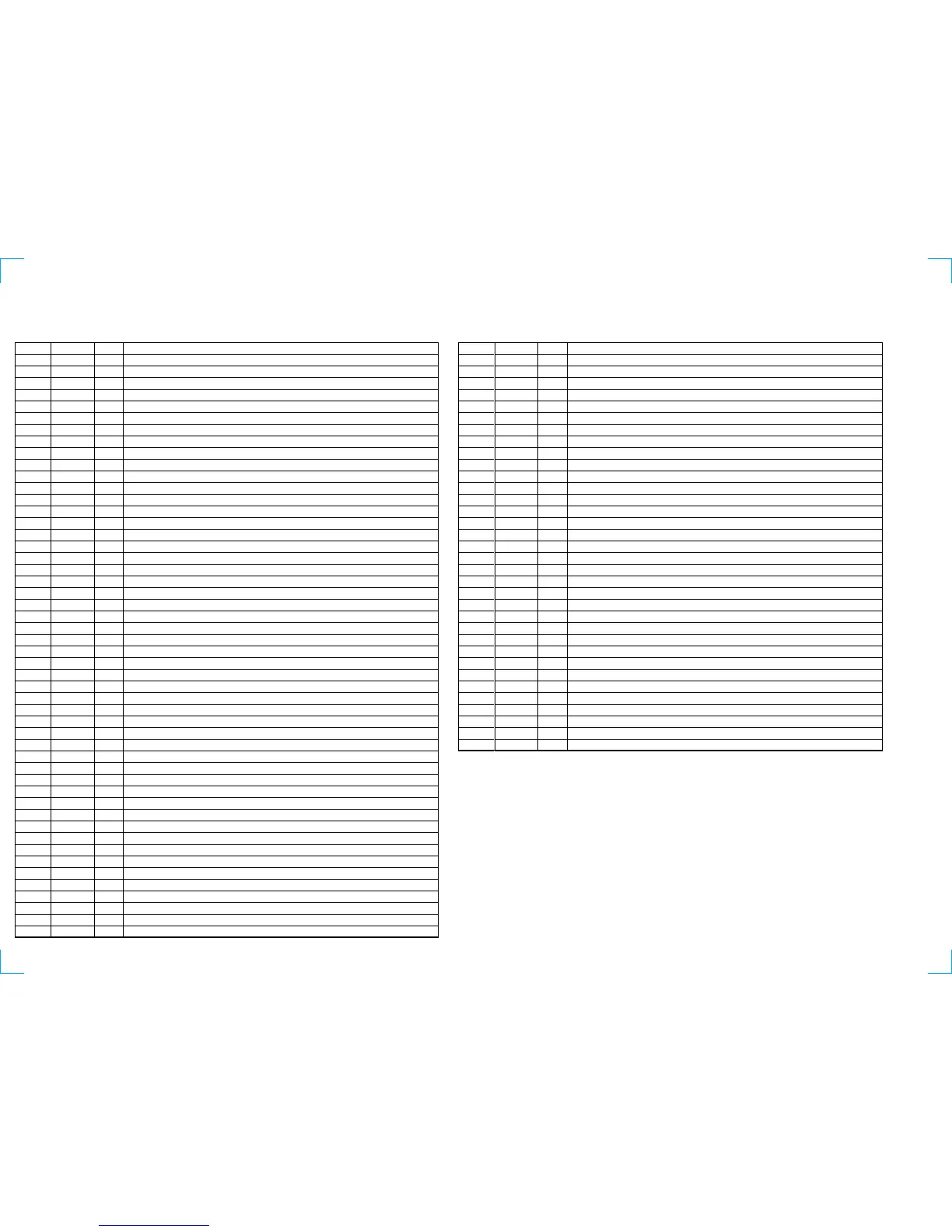

4-12. IC PIN FUNCTION DESCRIPTION

IC104 MN66710 DAB DECODER (MAIN BOARD)

Pin No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

I/O

O

O

I

I

O

I

I

I

I

I

I

—

—

I

O

O

I

O

O

O

O

O

O

O

I

O

O

I

O

—

—

I

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

—

—

O

Description

Microprocessor operation reference signal

PAD data ready signal

Microprocessor I/F data clock input

Microprocessor I/F received data input

Microprocessor I/F send data output

Microprocessor I/F mode

Test mode setting

Test mode setting

Test mode setting

Test mode setting

Master reset input

Digital VSS

Digital VDD

Master clock (23.576 MHz) input

Output of master clock oscillator circuit

SPDIF digital audio I/F output

Audio ADC serial data input

Audio AD/DA master clock

Audio AD/DA LR clock

Audio AD/DA serial clock output

Audio DAC serial data output

Auxiliary output for RD expansion

Auxiliary output for RD expansion

Auxiliary output for RD expansion

RD1 input

Auxiliary output for RD expansion

Auxiliary output for RD expansion

Auxiliary input for RD expansion

RD1 output

Digital VSS

Digital VDD

General purpose data output enable

General purpose data output window 4

General purpose data output window 3

General purpose data output window 2

General purpose data output window 1

General purpose data output window 0

General purpose data output clock

General purpose data output error flag

General purpose data output data

External DRAM address bit 4

External DRAM address bit 5

External DRAM address bit 6

External DRAM address bit 3

External DRAM address bit 2

External DRAM address bit 1

External DRAM address bit 0

Digital VSS

Digital VDD

External DRAM address bit 7

Pin Name

MPUSYNC

NPADRDY

MPUCLK

MPURX

MPUTX

MPUMOD

TEST0

TEST1

TEST2

TEST3

NRST

VSS0

VDD0

MCLK24

MCLK0

DAOUT

AUXDAT

SMCK

SLRCK

SCLK

SDAT

RDIU0

RDIU1

RDIU2

RDIIN

RDIU3

RDIU4

RDIU5

RDIOUT

VSS1

VDD1

FD3EN

FW4

FW3

FW2

FW1

FWFIC

FCLK3

FERF3

FDAT3

RAD4

RAD5

RAD6

RAD3

RAD2

RAD1

RAD0

VSS2

VDD2

RAD7

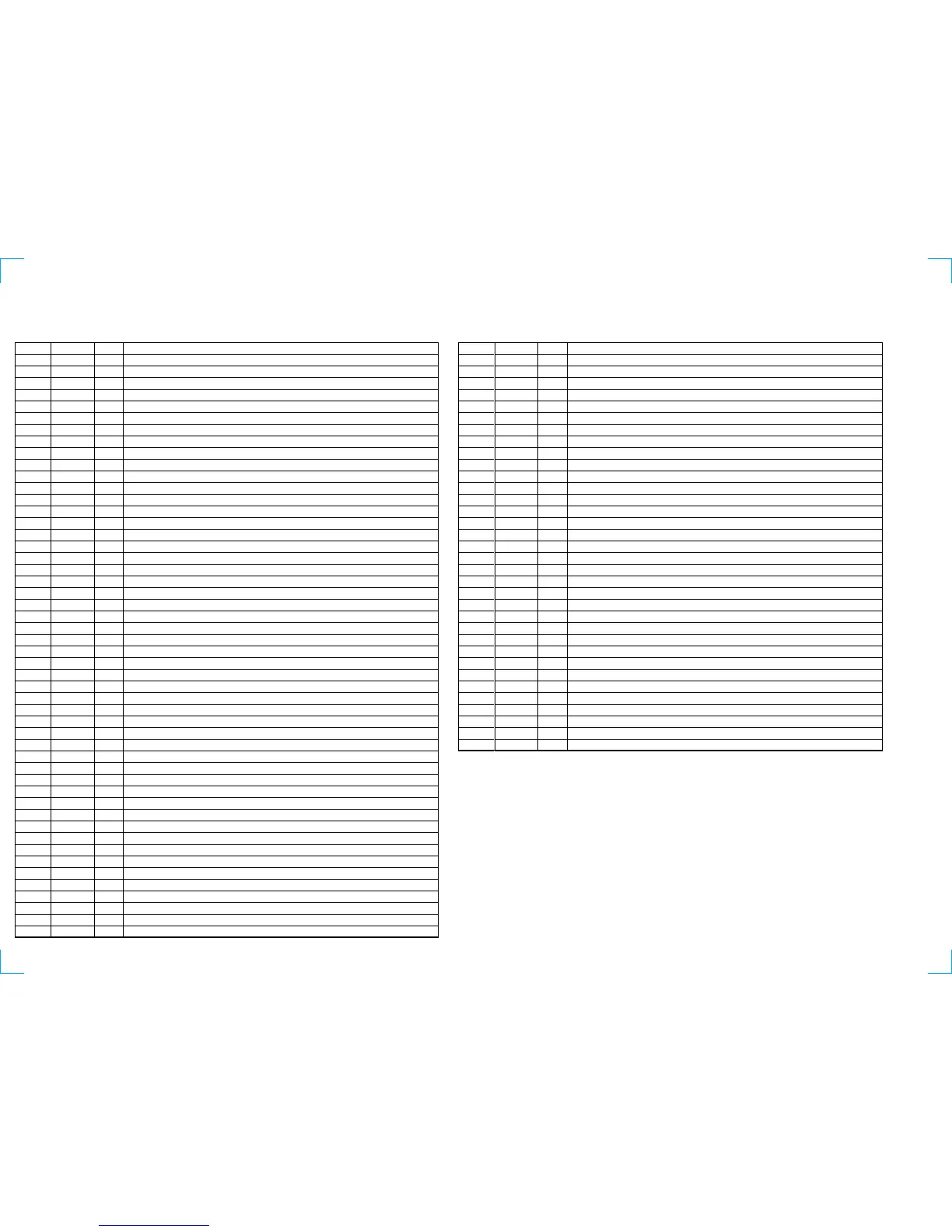

Pin No.

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

I/O

O

O

O

O

O

O

I/O

I/O

I/O

I/O

—

O

O

O

O

O

O

O

I

O

O

O

O

—

—

O

I

A

A

A

A

A

—

I

Description

External DRAM address bit 8

External DRAM output enable

External DRAM column address strobe

External DRAM address bit 9

External DRAM row address strobe

External DRAM write enable

External DRAM data bit 1

External DRAM data bit 0

External DRAM data bit 2

External DRAM data bit 3

Digital VSS

DSP monitor output bit 0

DSP monitor output bit 1

DSP monitor output bit 2

DSP monitor output bit 3

DSP monitor output bit 4

DSP monitor output bit 5

DSP monitor output bit 6

DSP monitor output enable

Sync signal output for CIR display

AFC/CIR DAC LR clock

AFC/CIR DAC clock

AFC/CIR DAC data

Digital VSS

Digital VDD

Frame sync signal output

NULL symbol detected signal input

Analog VSS

ADC bottom-side reference voltage

ADC analog input

ADC top-side reference voltage

Analog VDD

Reference power supply for 5 V input pad

Digital IQ generation selector input

Pin Name

RAD8

NRAMOE

NRCAS

RAD9

NRRAS

NRAMWE

RDT1

RDT0

RDT2

RDT3

VSS3

DSPMON0

DSPMON1

DSPMON2

DSPMON3

DSPMON4

DSPMON5

DSPMON6

DSPMNEN

CIRSYN

CTLLR

CTLCLK

CTLDAT

VSS4

VDD3

FSY0

NULDET

AV SS

ADVRB

ADIN

ADVRT

AV DD

VREF

IQMOD

Loading...

Loading...