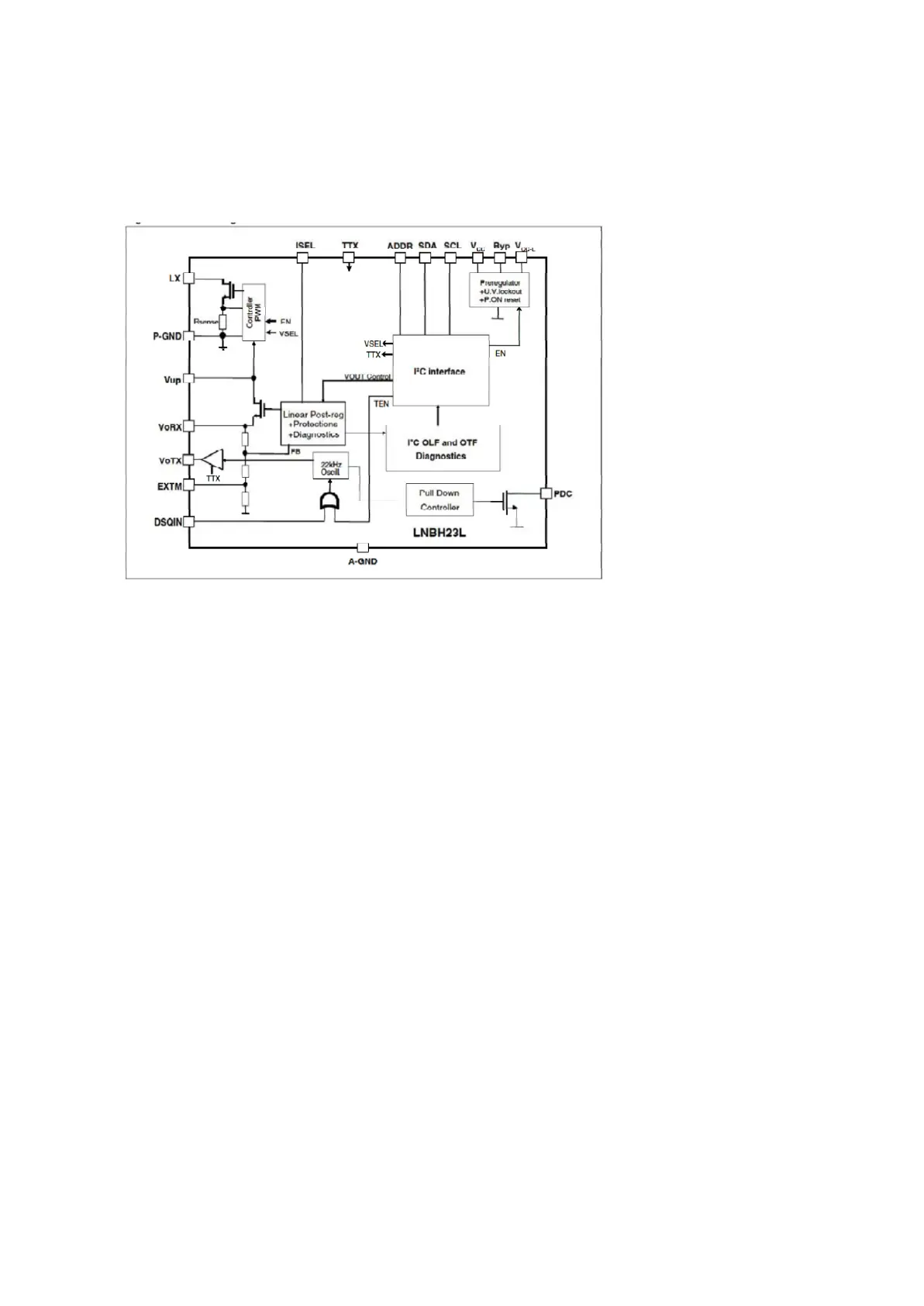

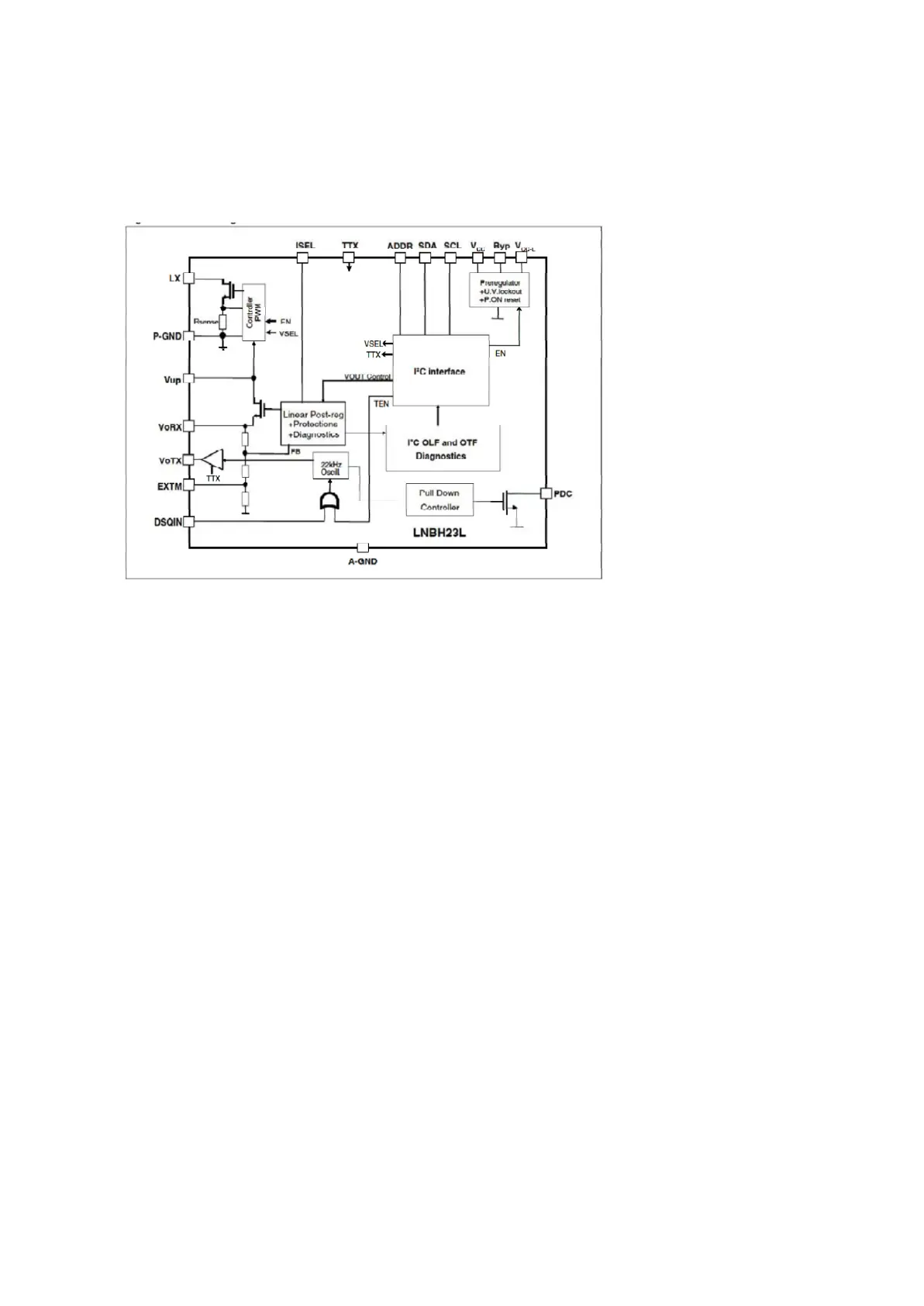

13.3 Block diagram

14 Advanced DVB-S/S2 demodulator M88DS3002 (U3)

14.1 Description

The M88DS3002 is an advanced single-chip demodulator for digital satellite television

broadcasting. It is fully compliant with the DVB-S/S2 standard and can support QPSK,

8PSK, 16APSK and 32APSK demodulation schemes. The chip provides a fast, easy-to-

apply and cost-effective front-end solution for digital satellite receiver. The M88DS3002

accepts baseband differential or single ended I and Q signals from a tuner, then

digitizes, demodulates and decodes the signals, and finally outputs an MPEG transport

stream. The M88DS3002 supports symbol rate from 1 Msps up to 45 Msps, and code

rate from 1/4 to 9/10. Its features cover blind scan, fade detection, timing and carrier

recovery, performance monitoring, co-channel interference cancellation, command

interface, and DiSEqC™ 2.X interface, etc. The device is controlled via a 2-wire serial

bus. The M88DS3002 works properly with 1.25 V and 3.3 V voltage supplies. Typically,

the power consumption is around 390 mW. The chip is available in a 64-pin QFN

package and is RoHS compliant.

14.2 Features

• Multi-standard demodulation

• Compliant with DVB-S/S2 specification

• QPSK, 8PSK, 16APSK and 32APSK demodulation schemes

• Maximum channel bit rate is 130 Mbps

• Maximum symbol rates are: 45 Msps for QPSK and 8PSK; 36 Msps for 16APSK

and 28 Msps for 32APSK

Loading...

Loading...