Line

I

is the

RAS*

output. As you can see,

it is

a

direct

function of

MREQ from the

CPU.

Z72, pins 4 and

5,

is

RAS*'s

buffer.

Line J,

MUX

is

sourced at Z69, pin

9,

through

buffer

Z72, pins 2 and 3.

Line

K,

CAS*, is

buffer-

ed by

Z72, pins 10

and

9,

and

is

a

function of QCAS, at

Z70, pin 6.

Notice the

following

sequence of events:

RAS* goes low

first.

MUX then

changes states.

CAS* then changes states

one clock

cycle later.

First, we get RAM address

select,

then MUX,

then we get

Column Select.

Hence,

the

first

part of the

address

we give the

RAMs will be the row

address.

We'll then flip

the switch

(multiplexer) and follow

with the

column address.

RAM ADDRESSING

In about the middle

of sheet

1,

on the left side

of the

RAM array,

multiplexers Z35 and

Z51

are

shown. On the

left side of

Z35, we find the area

where four address

lines

are

coming in. One

brace of four is

labeled

"0"

and

the

other

is labeled

"1

". Z51 is configured the same way

except

there

are only three

lines per brace.

The tells us that when

the

select pin is low,

the multiplexer will be

outputting data

associated with these

input lines. The

"1"

tells us the

opposite is

true. When the

select

pin

on the

multiplexer

goes high, it

will be outputting data

associated with the

"1"

input

address lines. The

select input for both

multiplexers

is pin 1. Z35,

therefore, operates

somewhat like a

4-pole,

double

throw switch,

where the select input (pin

1

)

is doing

the switching.

Z51 is used only as a

3-pole, double throw

switch

—

one

input/output is not

used. The enable input

to

the

multiplexer is pin 15. Since pin 15

is grounded on

both

IC's, the

"switches" are

always enabled.

READING

FROM

RAM

Assume the

CPU

needs

RAM data. Let's follow the

address-

ing and data

paths the

RAM will use. We'll use a 4K

RAM

example.

The

CPU outputs a

MREQ

and a

RD. The address

decoder

outputs

MEM*

and

RAM*.

MEM* activates the

RAM/ROM

data buffers

and

RAM* enables the chip select

(CS) for the

RAMs. At the

same time, the multiplexer

will load the

address into the

RAMs. RAS*

goes

low. The

MUX signal

is

low

at this time, so

A0 through A5 on the

RAM receive the

low

order address.

Notice that

RAS*

is buffered

by

Z68,

pins 14

and

13,

and is

applied

to

pin 4 of all the

RAMs. The

negative

going signal at pin 4

will load the lower

order

address in the

row section of each

RAM. A short time

later,

MUX changes state; it

goes high. The

multiplexer, Z35 and

Z51,

now switch and

the high order addresses

are applied to

the

RAMs. CAS*

will

now go

low.

CAS*

is

applied to

buffer Z67,

pin 14.

Pin 13

of

Z67 passes CAS* to pin 15

of

all

eight RAMs. On

the negative

transition of CAS*, the

high order

addresses (A6 through

A1

1)

will be

loaded in the

column

section of each

RAM. The

RAMs now

have the

entire address

from the

CPU. The RAM will now

output

data through the

buffers and

to the

CPU.

WRITING

TO RAM

The

difference between

a write

operation and a

read

opera-

tion is

exactly two

signals. Address

decoding

and address

multiplexing

work the same

way. During a

data

write, how-

ever, the

CPU

sends

data to the

RAMs. Hence, the

ROM/

RAM buffers are not

needed;

and

MEM* will not go

low.

Instead

of the

CPU issuing a

RD command,

it

supplies a

WR

instruction. WR*

is tied to

all eight

RAMs on pin

3.

When

this pin is

low, data

will be stored in

RAM

at

the

specified address.

When this

pin is high,

the

RAMs are in

read cycle.

REFRESHING

THE

RAMS

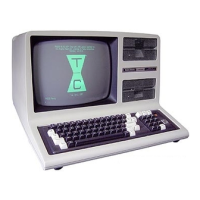

The TRS-80

uses

dynamic type

RAM. A

dynamic

RAM dif-

fers slightly

from a

static

RAM in data

retention.

A static

RAM will retain data

stored

in it so long

as power

is

applied

to it. A

dynamic

RAM

must be

periodically

addressed to

ensure

that it

retains the data

loaded

into it.

The

periodic

addressing is

called

refreshing.

You might

compare a

dyna-

mic

RAM with an

air-filled tire

with a slow

leak.

Every once

in a

while, the

tire must

be shot a

little

air so it won't go

flat.

If

we

did not

service

that tire, it

would

finally become

unusable.

The same

is true

about

dynamic RAM.

If the

system

does not

access the

RAMs every

so often,

they

will

"forget" data.

The

dynamic

RAM in

the TRS-80

uses an

"RAS Only"

type of

refresh.

In other words,

when RAS*

goes low, the

RAMs in the

system

will "refresh

themselves"

even

though

the

RAM

may

not be

in use at the

time.

A

s

stated before,

RAS

*

is gen

erated by

the

CPU

at pin

19

(MREQ). When-

ever

MREQ

goes

low,

RAS* goes

low; and the

RAMs

will

load

the lower

order address

into the row

section.

The

CPU

may be looking

at

system

ROM when

MREQ

goes

low,

but

RAM

will still

receive

RAS* and hence

be

"refreshed."

Normally, you

would not

be

too

concerned

about

this

aspect

of the

RAMs. But

you need to

be aware of the

dif-

ferences

between a

static

RAM and

a

dynamic

RAM.

Remember:

Dynamic

RAM must be

periodically

addressed

to

enable it to

retain data.

In the

TRS-80, the

RAM should

be refreshed

once

every two

milliseconds.

RAM

PROGRAMMING

You may

have

noticed X71

during the

discussion of the

RAM. X71

is a

DIP shunt.

It is used to

program the

size of

memory in a

system.

Find pin 13 on the

RAM.

Following

pin

13 down,

you

will see it is tied

to two

pins of

DIP

shunt X71.

Pin 13 of the

RAM is the

CE

(Chip

Enable) or

the A6

address input.

In a 4K

system, pins 4

and 13

of X71

12

Loading...

Loading...