Notice NOR

gate

Z30,

pins 8 and 9. These

pins

enable

Z30's output

to produce a signal called BLANK*. BLANK*

is used by the

video processor to give the 72 scan line

blanking for

the upper and lower boundaries. It

also defines

the blank boundaries

on the left and right of

the

screen.

VIDEO RAMS

The video RAMs

are

static

and hence do not need

refresh-

ing.

The

data bus is wired in the same way

as system

RAMs,

but with

a different enable signal. One interesting

point to

note: There

are seven RAMs. Six are used

for ASCII

storage, and the seventh is used

as a

graphic/alphanumeric

definition

bit. There are eight

data

lines.

Notice the line

labeled

Bit 6.

It

is sourced by NOR

gate

Z30

at pin 13. If

Bit 5 (Z62, pin

12) and

Bit 7 (Z63,

pin

12)

are low, then

Bit

6

will

be high.

Z30

is

a

sneaky

way of squeezing a

seventh ASCII bit out of six RAMs.

Aside from

the data bus, there is another RAM

output for

data. The video processor

needs video data for generation

of the alphanumeric

and graphic symbols. And this section

will be discussed

next.

VIDEO

PROCESSING

Video Processing consists of five

subsections. They

are:

data latch, character/graphic

generator, shift register,

sync

generator,

and video mixing/output driver. The

data latch

temporarily

stores an ASCII or graphic

word from video

RAM.

The latch will retain the byte

for processing

so that

the RAM is

free to

search

out

the

next byte. The

character

generator

is a

ROM

that is addressed by

the data latch

and

the

scan line signals. This ROM contains

the alphanumeric

format

that makes up all the characters. The

graphic

genera-

tor is not a ROM, but a 4-line-to-1-line

data multiplexer.

It

operates somewhat like a "bit steering" circuit.

It

steers an

ASCII word

into a graphic's symbol. The

shift register

accepts data from

the

character

generator

(or the graphic's

generator) and

converts parallel

dot

data

into

serial

dot

data. Meanwhile, the sync

generator circuits

have been

accepting

timing signals from the divider

chain. The

sync

circuits

shape up the

horizontal

and vertical

pulses, serrate

the vertical interval and

sends it all out to video

mixing in

serial

format.

In

the video mixing section,

the serial

dot

video and the serial sync

are brought together. The

result-

ing composite

video signal is then "fine

tuned"

in amplitude

and

dot-to-sync ratio, and then buffered

for a 75 ohm

output cable. The signal leaves

the

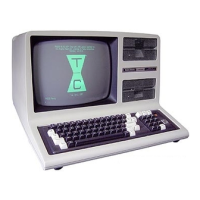

TRS-80

and is

applied

to the display.

In

the display, the signal is

torn apart into

its

separate

components, and you have

a

readable

image on the

screen.

DATA

LATCH

Z29,

the alphanumeric character generator and

to

Z8,

the

graphics generator. The inputs which control Z28

are on

pin 9 (latch) and pin 1 (VCLR*). The latch

signal at pin 9 is

a pulse train developed by

the

divider chain-input

condi-

tioning logic. This signal

goes

low every

six dot cycles (see

Figure

5 for latch timing). On the rising

edge of latch (low

to high transaction), ASCII data in RAM

is transferred to

the outputs

and

temporarily

stored by

Z28.

RAM data

at

the input

to

Z28 may now change,

and the

RAM

has time

to search for the next

ASCII

character. (RAM,

any

RAM,

has

a

parameter called "Access time".

This is the time it

takes for the data output

to

reflect

a change after an

address change. For example, assume

a

RAM

output is high.

The address

of

the RAM is changed

to a new location where

a

"0"

data bit is stored.

Even

though the RAM is

now

addressing the low cell, the output still

reads the previous

high. Only

after a

short length

of time

—

in the nano-

seconds

—

will the output change from a high

to a low.)

At the same time Z28 stored the ASCII

word, the divider

chain changed video

RAM

addresses. The RAM

is now

"looking"

for the next ASCII word. It

has

exactly

six dot

times

(about 560

nanoseconds

in 65

character

format) to

find

it before the

latch is

commanded

to store

the next

word.

Z27 is

a

smaller latch that operates in the exact same man-

ner

as

Z28. But instead of ASCII, it handles the graphic bit

and

blanking data.

Pin

4 is tied

to

the inverted output bit

from Z63, the graphic RAM.

Pin

5 of Z27 has signal

BLANK*

tied to it.

L8

is tied to pin 12 and our "sneaky"

bit, bit

6,

is tied to pin 13 of

Z27.

All of these signals are

latched into Z27

at

the same time

as

the ASCII word is

latched

into

Z28.

Each input

to

Z27 has

a

different function. The graphic bit

to pin

4

of

Z27 will determine if the ASCII word contained

inZ28 is an alphanumeric character or is

a

graphic word.

Pin

5 of Z27, is signal BLANK*. This signal comes from

Z30,

pin

10,

and controls the upper, lower, left and right

boun-

daries of the video display. When

BLANK* is high, the

CRT's electronic beam is allowed

to

draw on the screen.

When

BLANK*

is low, the beam is in a boundary area so

it

prevents the beam from drawing anything. L8 is connected

to pin 12 of

Z27. L8

acts somewhat like

BLANK*. L8,

remember,

specifies

where the electron beam

is located in

any character line. When low,

L8

allows the

beam

to out-

put alphanumeric dot data. When high, L8 shuts off the

beam because it

is

now

scanning one of the five scan lines

between character lines.

The

last piece of data

comes into

Z27

at

pin 13. Sourced

at

Z30, pin

13,

this is the "sneaky

bit" that is derived from data contained in

RAMs Z63

and

Z62. This is the only bit at

Z27

which

could

be

considered

part of the

ASCII

word.

The output is applied

to

character

generator Z29,

at

pin 1.

The data latch consists of Z28 for the ASCII

and

Z27

for

the graphic bit and blanking signals. The

inputs of Z28

come

from the six video

RAMs. The

outputs of Z28

go to

Notice

pin 1 of both data

latches.

This

input, when low,

will force

the latches

to

their clear

state (zero

at

the out-

puts). This signal is called VCLR*

(Video Clear) and is

17

Loading...

Loading...