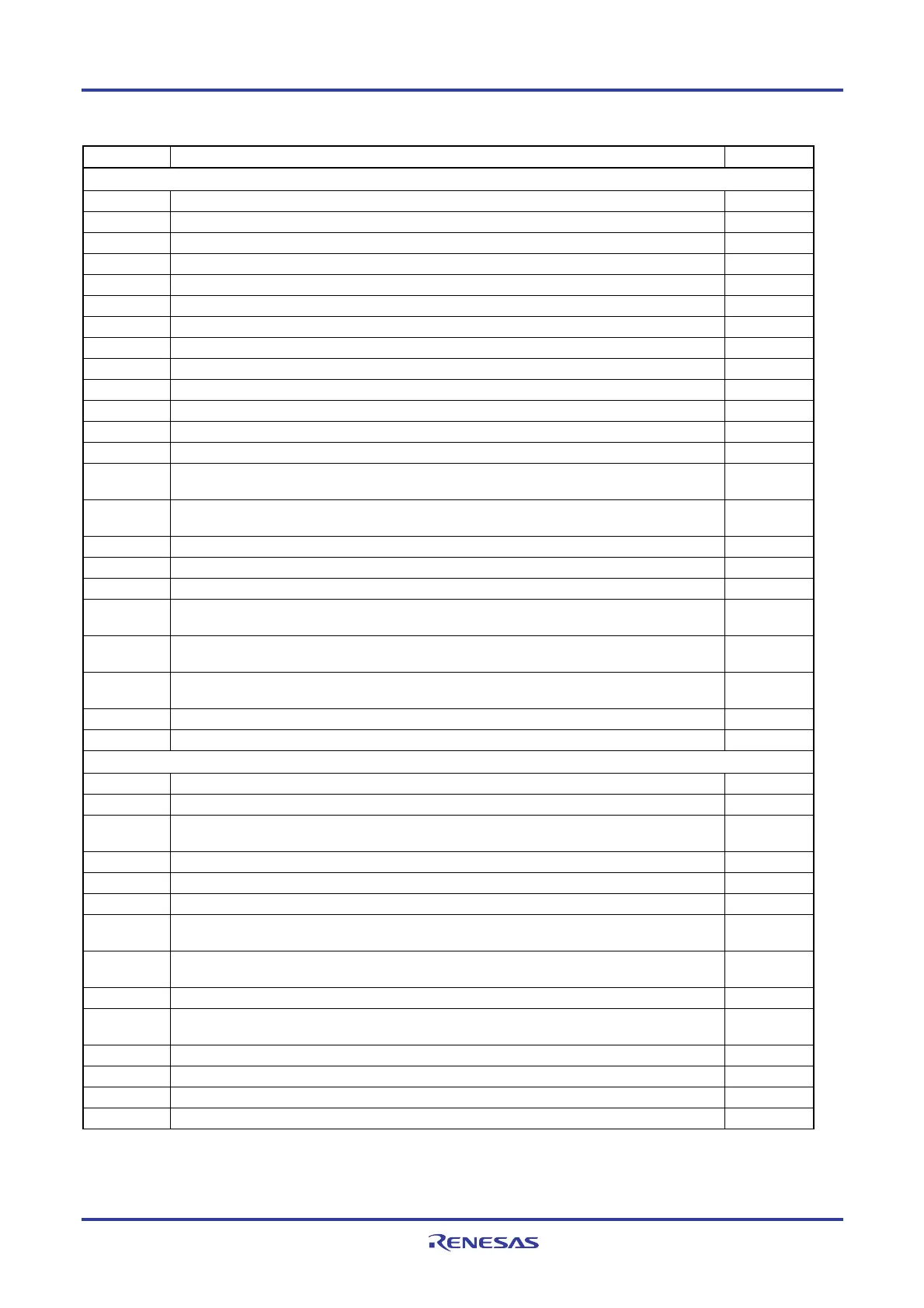

RL78/G13 APPENDIX A REVISION HISTORY

R01UH0146EJ0100 Rev.1.00 1063

Sep 22, 2011

(2/7)

Page Description Classification

CHAPTER 4 PORT FUNCTIONS

Though out Addition of Table 4-x. Settings of Registers When Using Port x (c)

Though out Change of Block Diagram in 4.2 Port Configuration to be corresponded to 128-pin products (c)

Though out Change of description for Digital I/O/analog input in 4.2 Port Configuration (c)

Though out Change of description for reset signal generation in 4.2 Port Configuration (c)

p. 180 Change of Figure 4-10. Block Diagram of P13 (c)

p. 186 Change of Figure 4-15. Block Diagram of P20 to P27 (c)

p. 197 Change of Figure 4-23. Block Diagram of P43, P44 (a)

p. 199 Change of Figure 4-25. Block Diagram of P46 (a)

p. 200 Change of Figure 4-26. Block Diagram of P47 (a)

p. 236 Change of Figure 4-52. Block Diagram of P121 and P122 (c)

p. 237 Change of Figure 4-53. Block Diagram of P123 and P124 (c)

p. 239 Change of description in 4.2.14 Port 13 (c)

p. 250 Change of Figure 4-64. Block Diagram of P150 to P156 (c)

p. 251, 252 Change of Table 4-21. PMxx, Pxx, PUxx, PIMxx, POMxx, PMCxx registers and the bits

mounted on each product (20-pin products to 64-pin products)

(c)

p. 256 Change of Table 4-22. PMxx, Pxx, PUxx, PIMxx, POMxx, PMCxx registers and the bits

mounted on each product (80-pin products to 128-pin products) (3/4)

(c)

p. 265 Change of Figure 4-70. Format of Port Mode Control Register (c)

p. 268 Change of cautions 1 and 2 in Figure 4-72. Format of Peripheral I/O Redirection Register (PIOR) (c)

p. 269 Change of description in 4.3 (9) Global digital input disable register (GDIDIS) (c)

p. 271, 272 Change of description in 4.4.4 Connecting to external device with different potential (1.8 V,

2.5 V, 3 V)

(c)

p. 273 to 277 Change of Table 4-23. Settings of Port Mode Register, and Output Latch When Using

Alternate Function

(b), (c)

p. 278 Addition of note 3 to Table 4-23. Settings of Port Mode Register, and Output Latch When

Using Alternate Function

(c)

p. 279 Addition of 4.6 Cautions When Using Port Function (c)

p. 280, 281 Addition of 4.6.2 Cautions on the pin settings on the products other than 128-pin (c)

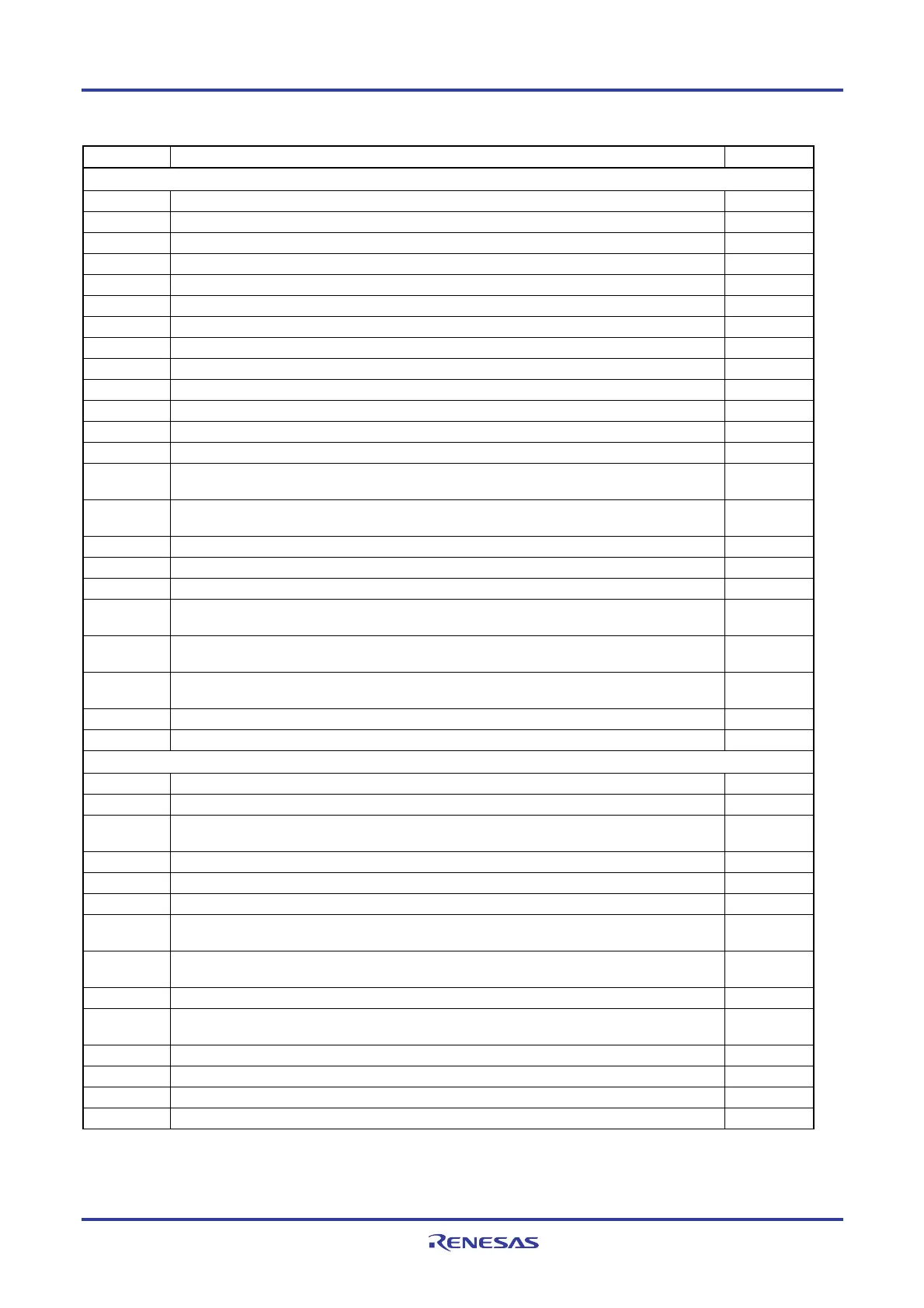

CHAPTER 5 CLOCK GENERATOR

p. 283 Change of description in 5.1 (2) Subsystem clock (c)

p. 285 Change of Figure 5-1. Block Diagram of Clock Generator (c)

p. 287 Change and addition of note to Figure 5-2. Format of Clock Operation Mode Control Register

(CMC)

(c)

p. 289 Change of description and deletion of note 2 in 5.3 (2) System clock control register (CKC) (c)

p. 295 Change of Figure 5-6. Format of Oscillation Stabilization Time Select Register (OSTS) (c)

p. 296 Deletion of note 4 in Figure 5-7. Format of Peripheral Enable Register 0 (PER0) (c)

p. 299 Change of description and deletion of caution in 5.3 (7) Operation speed mode control register

(OSMC)

(c)

p. 300 Change of cautions 2, 3 in Figure 5-9. Format of High-speed On-chip Oscillator Frequency

Select Register (HOCODIV)

(c)

p. 301 Change of 5.3 (9) High-speed on-chip oscillator trimming register (HIOTRM) (c)

p. 308 Addition of note 3 to Figure 5-14. Clock Generator Operation When Power Supply Voltage Is

Turned On

(c)

p. 309 Change of 5.6.1 Example of setting high-speed on-chip oscillator (c)

p. 310 Change of description in 5.6.2 Example of setting X1 oscillation clock (c)

p. 315 Change of (6) and (8) in Table 5-3. CPU Clock Transition and SFR Register Setting Examples (c)

p. 320 Change of Table 5-6 and Table 5-7 (c)

Remark “Classification” in the above table classifies revisions as follows.

(a): Error correction, (b): Addition/change of specifications, (c): Addition/change of description or note,

(d): Addition/change of package, part number, or management division, (e): Addition/change of related

documents

Loading...

Loading...