RL78/G13 CHAPTER 14 MULTIPLIER AND DIVIDER/MULTIPLY-ACCUMULATOR

R01UH0146EJ0100 Rev.1.00 790

Sep 22, 2011

14.3 Register Controlling Multiplier and Divider/Multiply-Accumulator

The multiplier and divider/multiply-accumulator is controlled by using the multiplication/division control register (MDUC).

(1) Multiplication/division control register (MDUC)

The MDUC register is an 8-bit register that controls the operation of the multiplier and divider/multiply-accumulator.

The MDUC register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

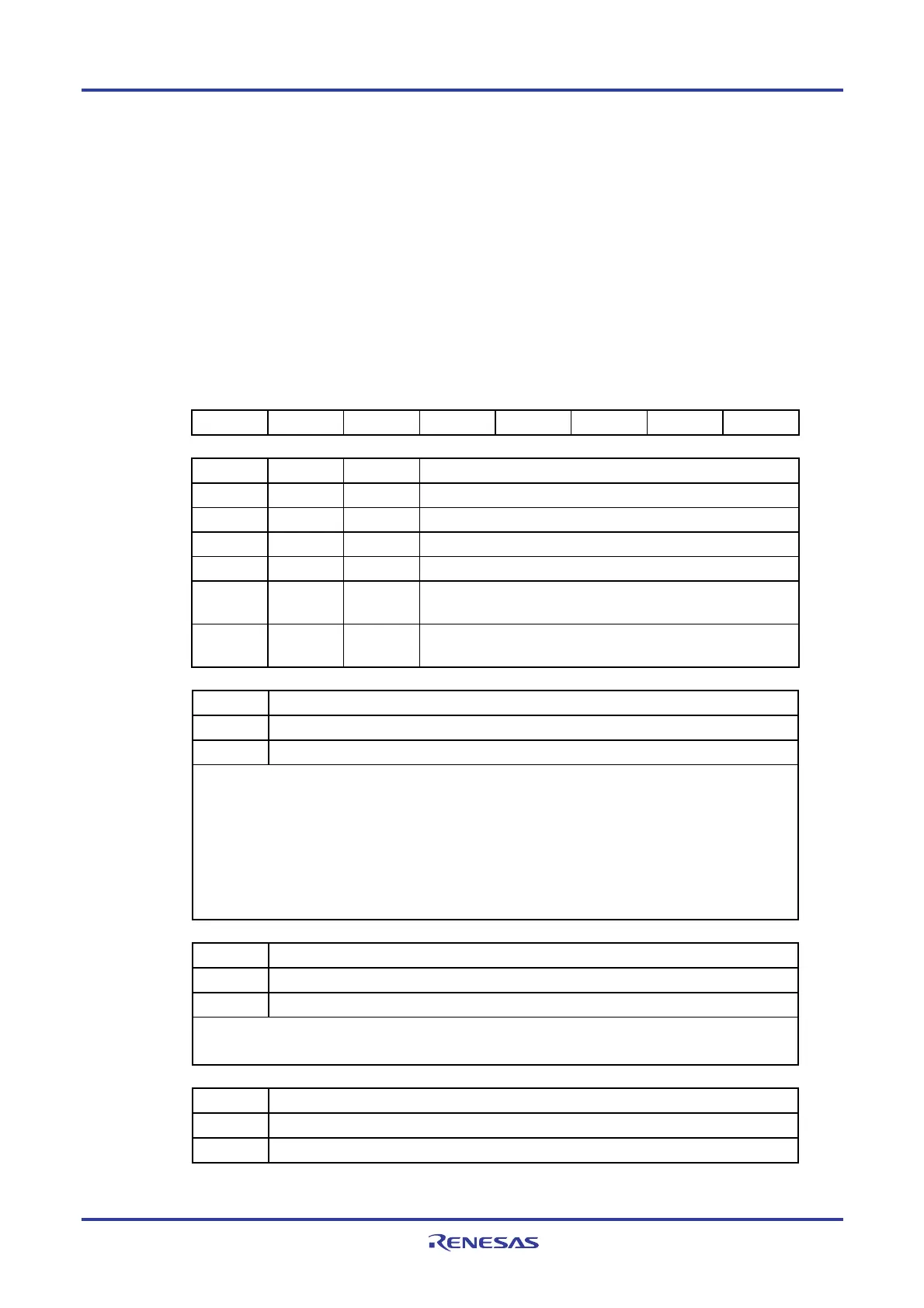

Figure 14-5. Format of Multiplication/Division Control Register (MDUC)

Address: F00E8H After reset: 00H R/W

Symbol <7> <6> 5 4 <3> <2> <1> <0>

MDUC DIVMODE MACMODE 0 0 MDSM MDCOF MACSF DIVST

DIVMODE MACMODE MDSM Operation mode selection

0 0 0 Multiplication mode (unsigned) (default)

0 0 1 Multiplication mode (signed)

0 1 0 Multiply-accumulator mode (unsigned)

0 1 1 Multiply-accumulator mode (signed)

1 0 0

Division mode (unsigned), generation of a division completion

interrupt (INTMD)

1 1 0

Division mode (unsigned), not generation of a division completion

interrupt (INTMD)

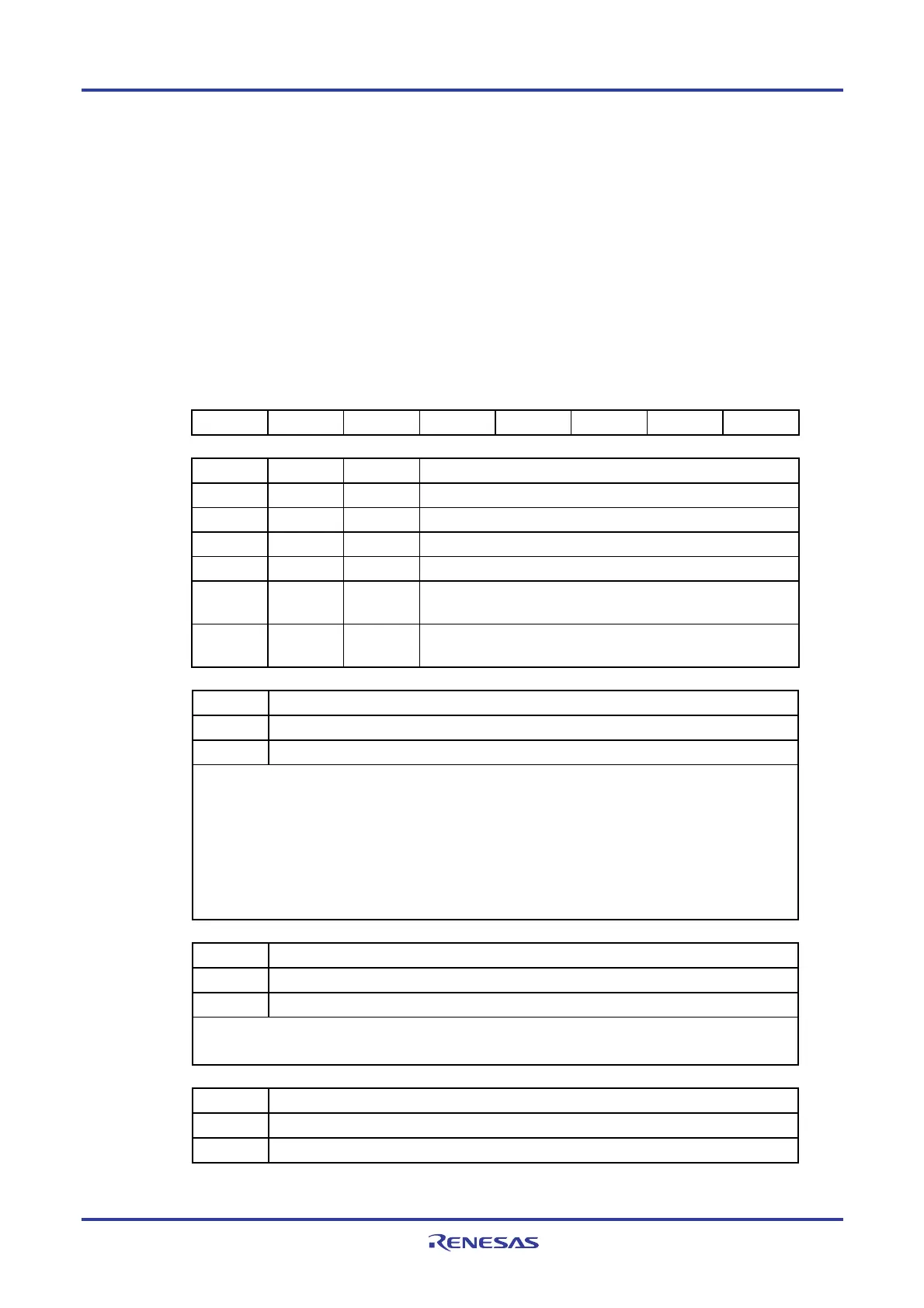

MACOF Overflow flag of multiply-accumulation result (accumulated value)

0 No overflow

1 With over flow

<Set condition>

• For the multiply-accumulator mode (unsigned)

The bit is set when the accumulated value goes outside the range from 00000000h to FFFFFFFFh.

• For the multiply-accumulator mode (signed)

The bit is set when the result of adding a positive product to a positive accumulated value exceeds

7FFFFFFFh and is negative, or when the result of adding a negative product to a negative accumulated

value exceeds 80000000h and is positive.

MACSF Sign flag of multiply-accumulation result (accumulated value)

0 The accumulated value is positive.

1 The accumulated value is negative.

Multiply-accumulator mode (unsigned): The bit is always 0.

Multiply-accumulator mode (signed): The bit indicates the sign bit of the accumulated value.

DIVST

Note

Division operation start/stop

0 Division operation processing complete

1 Starts division operation/division operation processing in progress

Loading...

Loading...