RL78/G13 CHAPTER 4 PORT FUNCTIONS

R01UH0146EJ0100 Rev.1.00 261

Sep 22, 2011

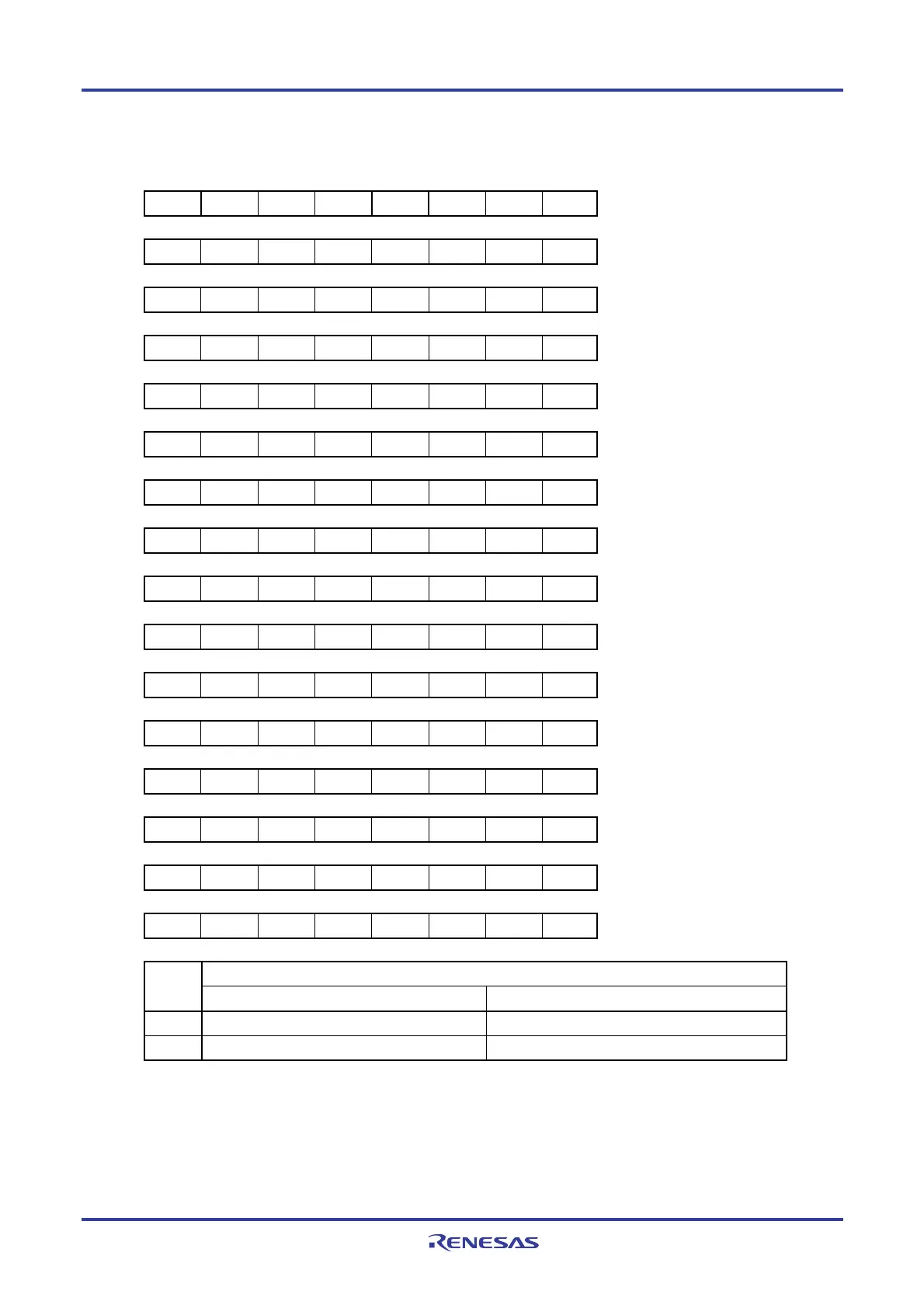

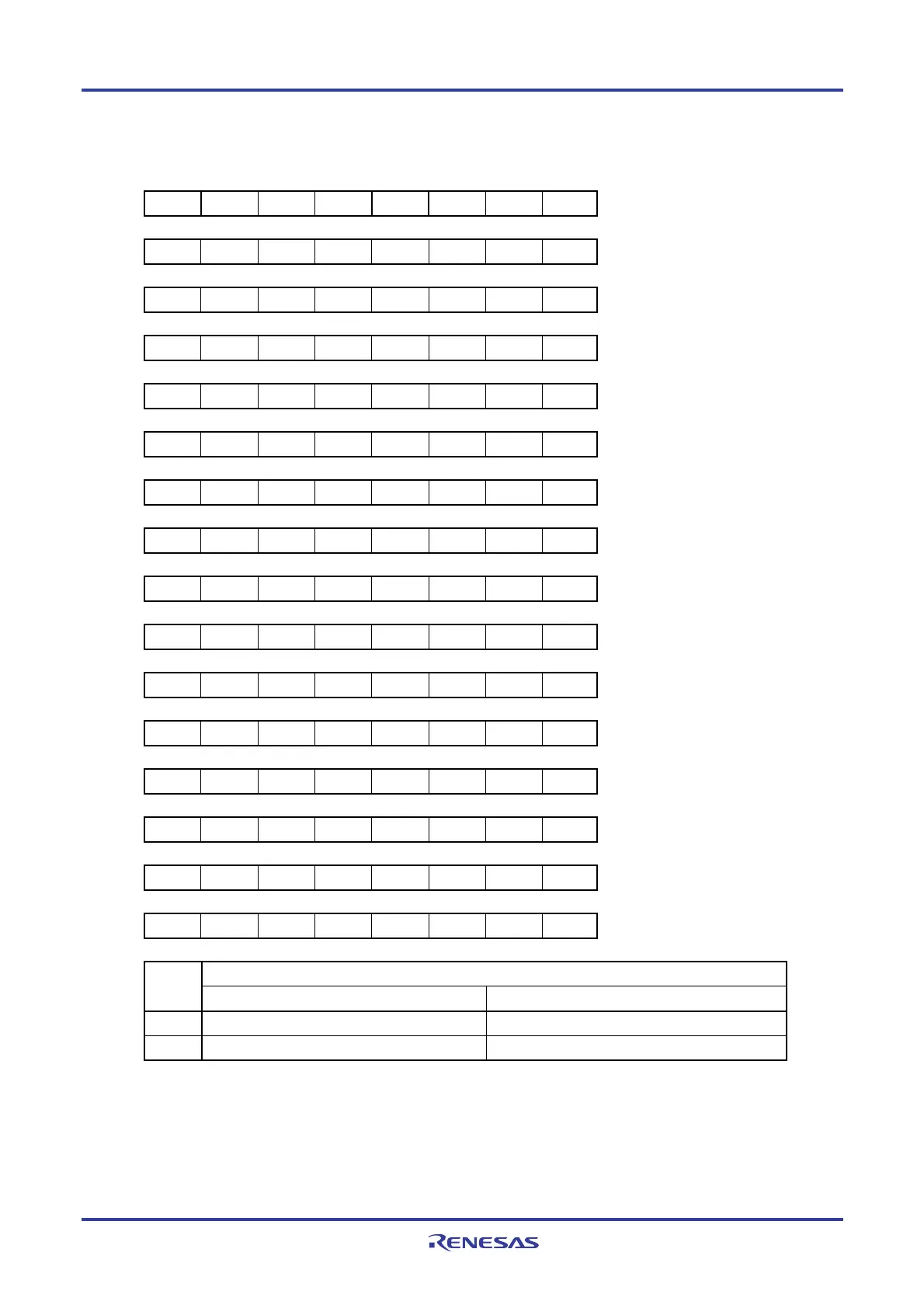

Figure 4-66. Format of Port Register (128-pin products)

Symbol 7 6 5 4 3 2 1 0 Address After reset R/W

P0 P07 P06 P05 P04 P03 P02 P01 P00 FFF00H 00H (output latch) R/W

P1 P17 P16 P15 P14 P13 P12 P11 P10 FFF01H 00H (output latch) R/W

P2 P27 P26 P25 P24 P23 P22 P21 P20 FFF02H 00H (output latch) R/W

P3 P37 P36 P35 P34 P33 P32 P31 P30 FFF03H 00H (output latch) R/W

P4 P47 P46 P45 P44 P43 P42 P41 P40 FFF04H 00H (output latch) R/W

P5 P57 P56 P55 P54 P53 P52 P51 P50 FFF05H 00H (output latch) R/W

P6 P67 P66 P65 P64 P63 P62 P61 P60 FFF06H 00H (output latch) R/W

P7 P77 P76 P75 P74 P73 P72 P71 P70 FFF07H 00H (output latch) R/W

P8 P87 P86 P85 P84 P83 P82 P81 P80 FFF08H 00H (output latch) R/W

P9 P97 P96 P95 P94 P93 P92 P91 P90 FFF09H 00H (output latch) R/W

P10 0 P106 P105 P104 P103 P102 P101 P100 FFF0AH 00H (output latch) R/W

P11 P117 P116 P115 P114 P113 P112 P111 P110 FFF0BH 00H (output latch) R/W

P12 P127 P126 P125 P124 P123 P122 P121 P120 FFF0CH Undefined R/W

Note

P13 P137 0 0 0 0 0 0 P130 FFF0DH Undefined R/W

Note

P14 P147 P146 P145 P144 P143 P142 P141 P140 FFF0EH 00H (output latch) R/W

P15 0 P156 P155 P154 P153 P152 P151 P150 FFF0FH 00H (output latch) R/W

m = 0 to 15; n = 0 to 7 Pmn

Output data control (in output mode) Input data read (in input mode)

0 Output 0 Input low level

1 Output 1 Input high level

Note P121 to P124, and P137 are read-only.

Loading...

Loading...