RL78/G13 CHAPTER 12 SERIAL ARRAY UNIT

R01UH0146EJ0100 Rev.1.00 564

Sep 22, 2011

(14) Serial standby control register m (SSCm)

The SSC0 register is used to control the startup of reception (the SNOOZE mode) while in the STOP mode when

receiving CSI00 or UART0 serial data.

The SSC1

Note

register is used to control the startup of reception (the SNOOZE mode) while in the STOP mode

when receiving CSI20 or UART2 serial data.

The SSCm register can be set by a 16-bit memory manipulation instruction.

The lower 8 bits of the SSCm register can be set with an 8-bit memory manipulation instruction with SSCmL.

Reset signal generation clears the SSCm register to 0000H.

Note The SSC1 register is provided in the 80, 100, 128-pin products only.

Caution The maximum transfer rate in the SNOOZE mode is as follows.

• When using CSI00, CSI20 : 1 Mbps (target)

• When using UART0, UART2 : 9600 bps (target)

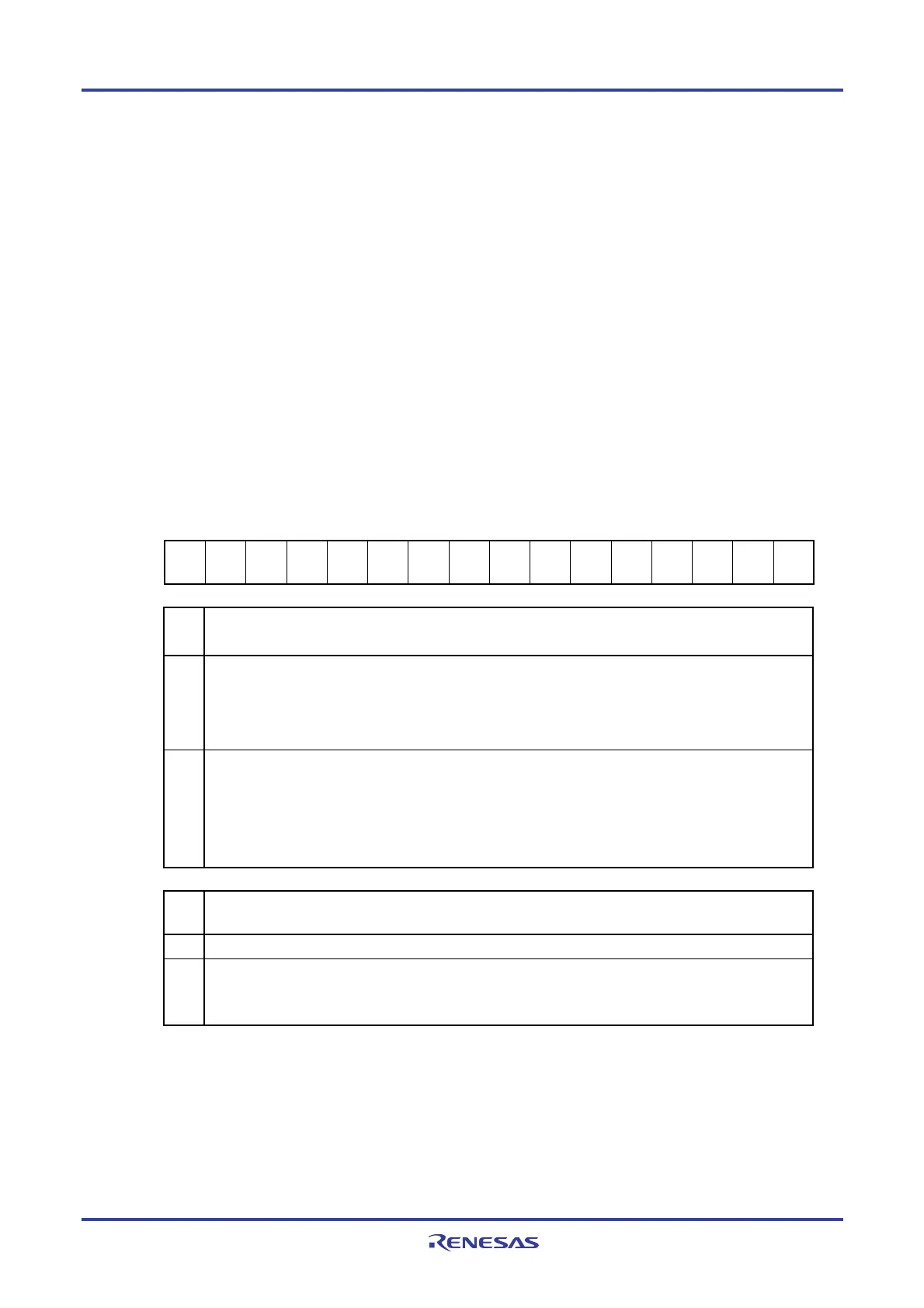

Figure 12-18. Format of Serial Standby Control Register m (SSCm)

Address: F0138H (SSC0), F0178H (SSC1) After reset: 0000H R/W

Symbol 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SSCm 0 0 0 0 0 0 0 0 0 0 0 0 0 0

SS

ECm

SWC

m

SS

ECm

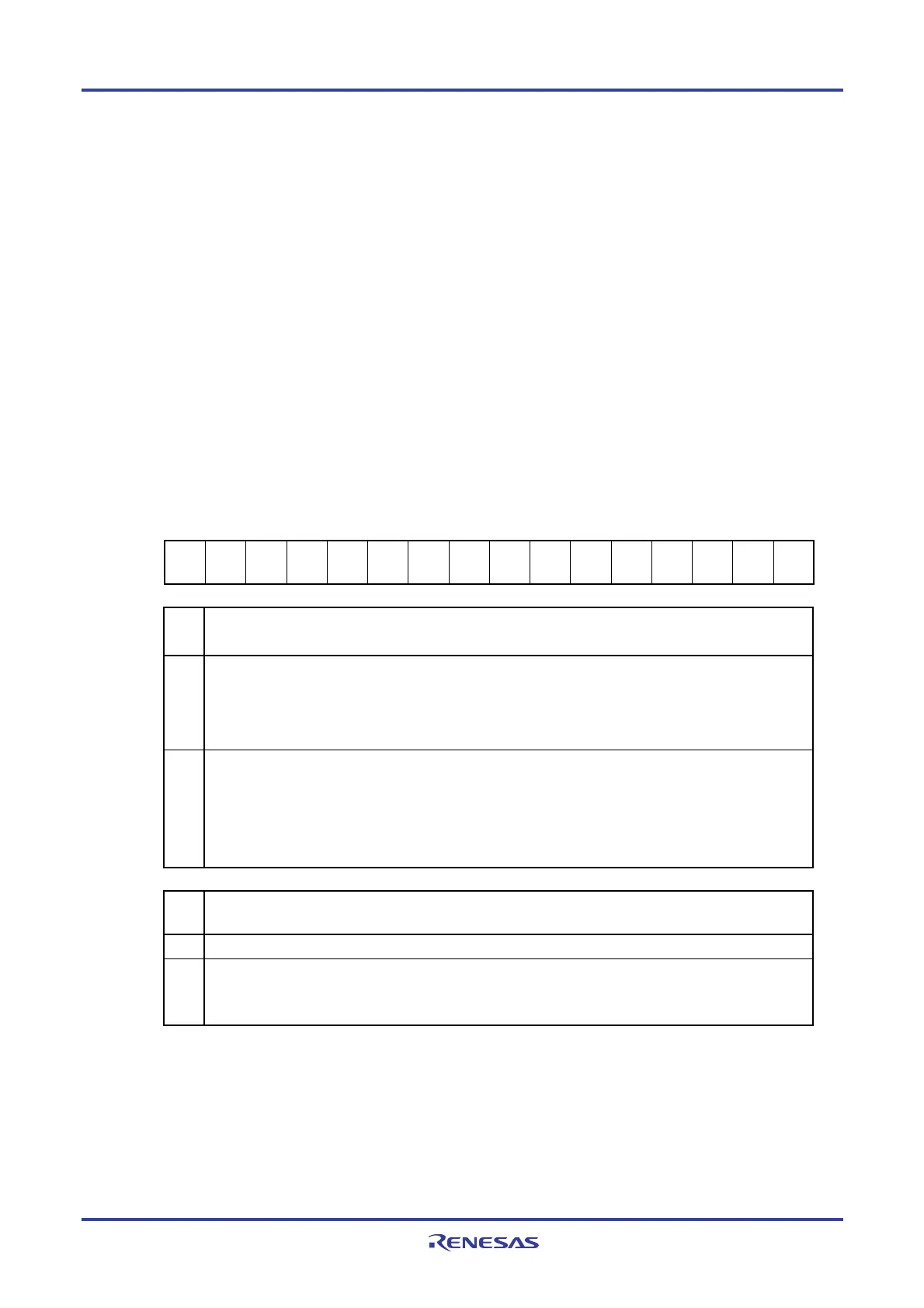

Selection of whether to enable or stop the generation of transfer end interrupts

0 Enable the generation of error interrupts (INTSRE0/INTSRE2).

In the following cases, the clock request signal (an internal signal) to the clock generator is also cleared:

• When the SWC bit is cleared to 0

• When the UART reception start bit is mistakenly detected

1 Stop the generation of error interrupts (INTSRE0/INTSRE2).

In the following cases, the clock request signal (an internal signal) to the clock generator is also cleared:

• When the SWCm bit is cleared to 0

• When the UART reception start bit is mistakenly detected

• When the transfer end interrupt generation timing is based on a parity error or framing error

SW

Cm

Selection of whether to enable or stop the startup of CSI00/CSI20 or UART0/UART2 reception while in the

STOP mode

0 Stop the startup of reception while in the STOP mode.

1 Enable the startup of reception while in the STOP mode.

(During asynchronous CSI00/CSI20 reception or UART0/UART2 reception, the baud rate adjustment

function is enabled.)

Caution Setting SSECm, SWCm = 1, 0 is prohibited.

<R>

<R>

Loading...

Loading...