RL78/G13 CHAPTER 15 DMA CONTROLLER

R01UH0146EJ0100 Rev.1.00 805

Sep 22, 2011

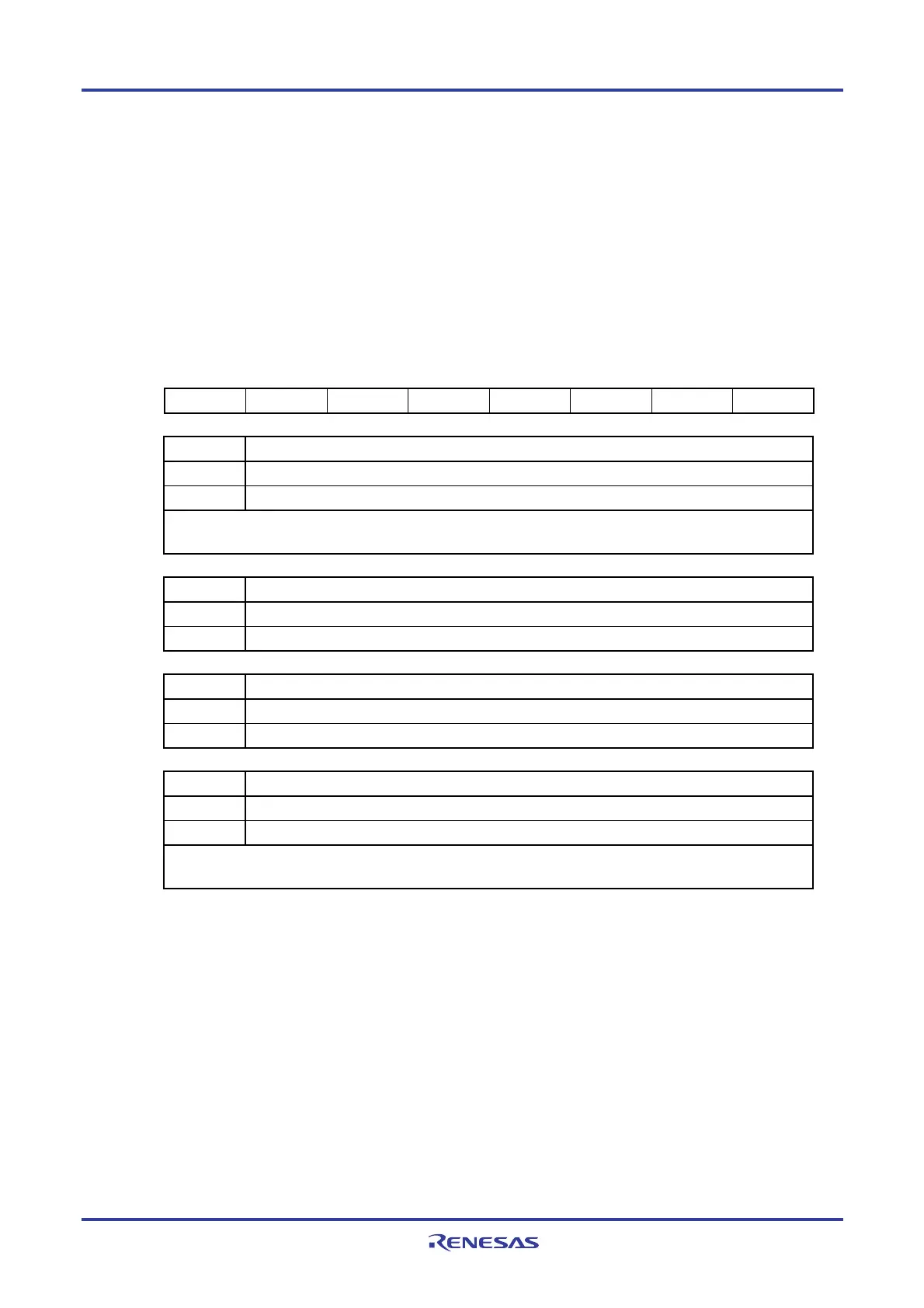

(1) DMA mode control register n (DMCn)

The DMCn register is a register that is used to set a transfer mode of DMA channel n. It is used to select a

transfer direction, data size, setting of pending, and start source. Bit 7 (STGn) is a software trigger that starts

DMA.

Rewriting bits 6, 5, and 3 to 0 of the DMCn register is prohibited during operation (when DSTn = 1).

The DMCn register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

Figure 15-4. Format of DMA Mode Control Register n (DMCn) (1/3)

Address: FFFBAH (DMC0), FFFBBH (DMC1), F020AH (DMC2), F020BH (DMC3) After reset: 00H R/W

Symbol <7> <6> <5> <4> 3 2 1 0

DMCn STGn DRSn DSn DWAITn IFCn3 IFCn2 IFCn1 IFCn0

STGn

Note 1

DMA transfer start software trigger

0 No trigger operation

1 DMA transfer is started when DMA operation is enabled (DENn = 1).

DMA transfer is performed once by writing 1 to the STGn bit when DMA operation is enabled (DENn = 1).

When this bit is read, 0 is always read.

DRSn Selection of DMA transfer direction

0 SFR to internal RAM

1 Internal RAM to SFR

DSn Specification of transfer data size for DMA transfer

0 8 bits

1 16 bits

DWAITn

Note 2

Pending of DMA transfer

0 Executes DMA transfer upon DMA start request (not held pending).

1 Holds DMA start request pending if any.

DMA transfer that has been held pending can be started by clearing the value of the DWAITn bit to 0.

It takes 2 clocks to actually hold DMA transfer pending when the value of the DWAITn bit is set to 1.

Notes 1. The software trigger (STGn) can be used regardless of the IFCn0 to IFCn3 bits values.

2. When DMA transfer is held pending while using two or more DMA channels, be sure to hold the DMA

transfer pending for all channels (by setting the DWAIT0, DWAIT1, DWAIT2, and DWAIT3 bits to 1).

Remark n: DMA channel number (n = 0 to 3)

Loading...

Loading...