RL78/G13 CHAPTER 18 STANDBY FUNCTION

R01UH0146EJ0100 Rev.1.00 864

Sep 22, 2011

Cautions 1. To use the peripheral hardware that stops operation in the STOP mode, and the peripheral hardware

for which the clock that stops oscillating in the STOP mode after the STOP mode is released, restart

the peripheral hardware.

2. To stop the low-speed on-chip oscillator clock in the STOP mode, must previously be set an option

byte to stop the watchdog timer operation in the HALT/STOP mode (bit 0 (WDSTBYON) of 000C0H =

0).

3. To shorten oscillation stabilization time after the STOP mode is released when the CPU operates

with the high-speed system clock (X1 oscillation), temporarily switch the CPU clock to the high-

speed on-chip oscillator clock before the execution of the STOP instruction. Before changing the

CPU clock from the high-speed on-chip oscillator clock to the high-speed system clock (X1

oscillation) after the STOP mode is released, check the oscillation stabilization time with the

oscillation stabilization time counter status register (OSTC).

(2) STOP mode release

The STOP mode can be released by the following two sources.

(a) Release by unmasked interrupt request

When an unmasked interrupt request is generated, the STOP mode is released. After the oscillation stabilization

time has elapsed, if interrupt acknowledgment is enabled, vectored interrupt servicing is carried out. If interrupt

acknowledgment is disabled, the next address instruction is executed.

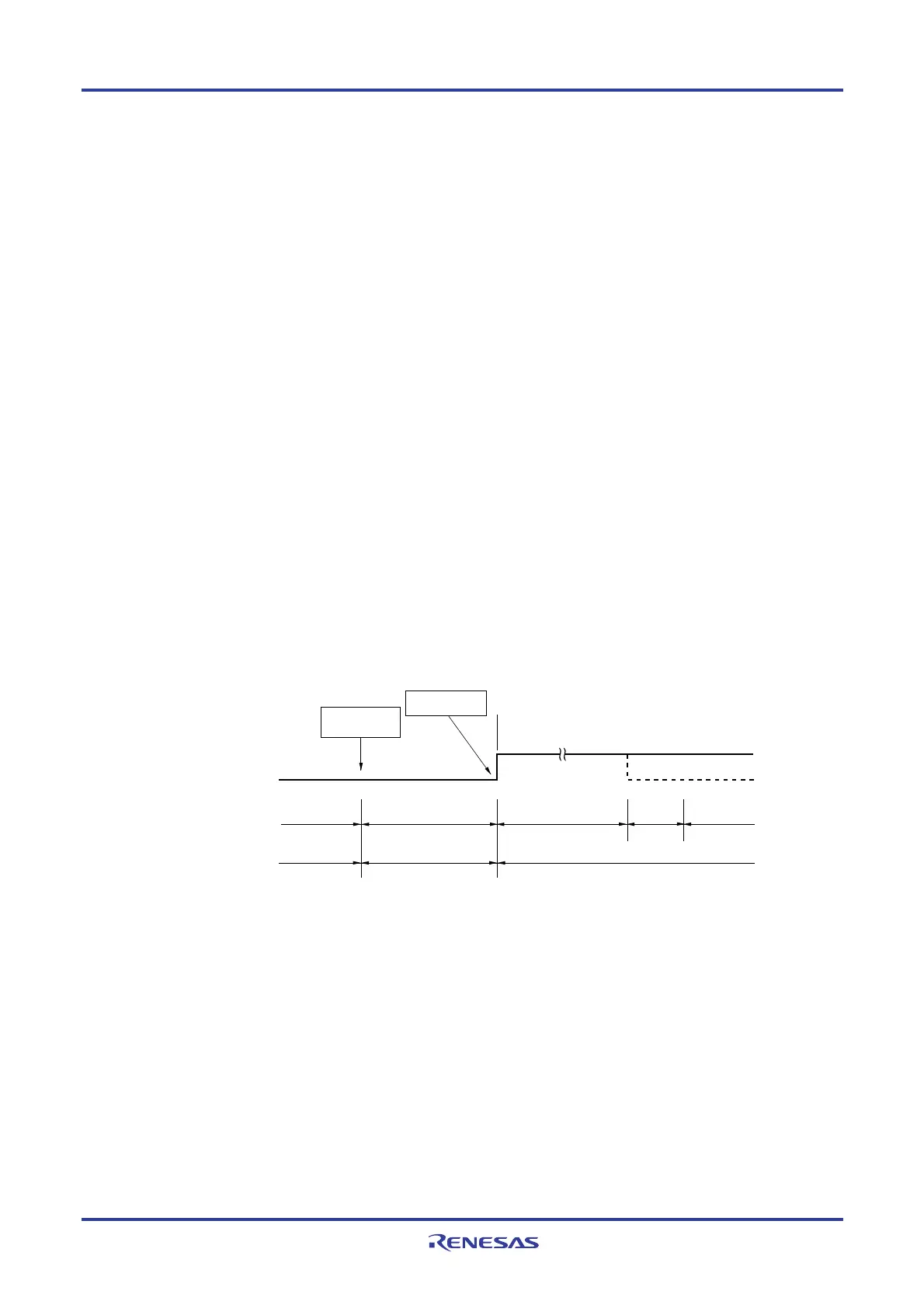

Figure 18-5. STOP Mode Release by Interrupt Request Generation (1/2)

(1) When high-speed system clock (X1 oscillation) is used as CPU clock

Normal operation

(high-speed

system clock)

Normal operation

(high-speed

system clock)

OscillatesOscillates

STOP

instruction

STOP mode

Standby release signal

Oscillation stopped

High-speed

system clock

(X1 oscillation)

Status of CPU

Oscillation

stabilization time

(set by OSTS)

Interrupt

request

Wait

Note

Note Wait time for STOP mode release

• High-speed system clock (X1 oscillation): 3-clock

Remark The broken lines indicate the case when the interrupt request that has released the standby mode is

acknowledged.

<R>

<R>

Loading...

Loading...