47

LC-30HV4E

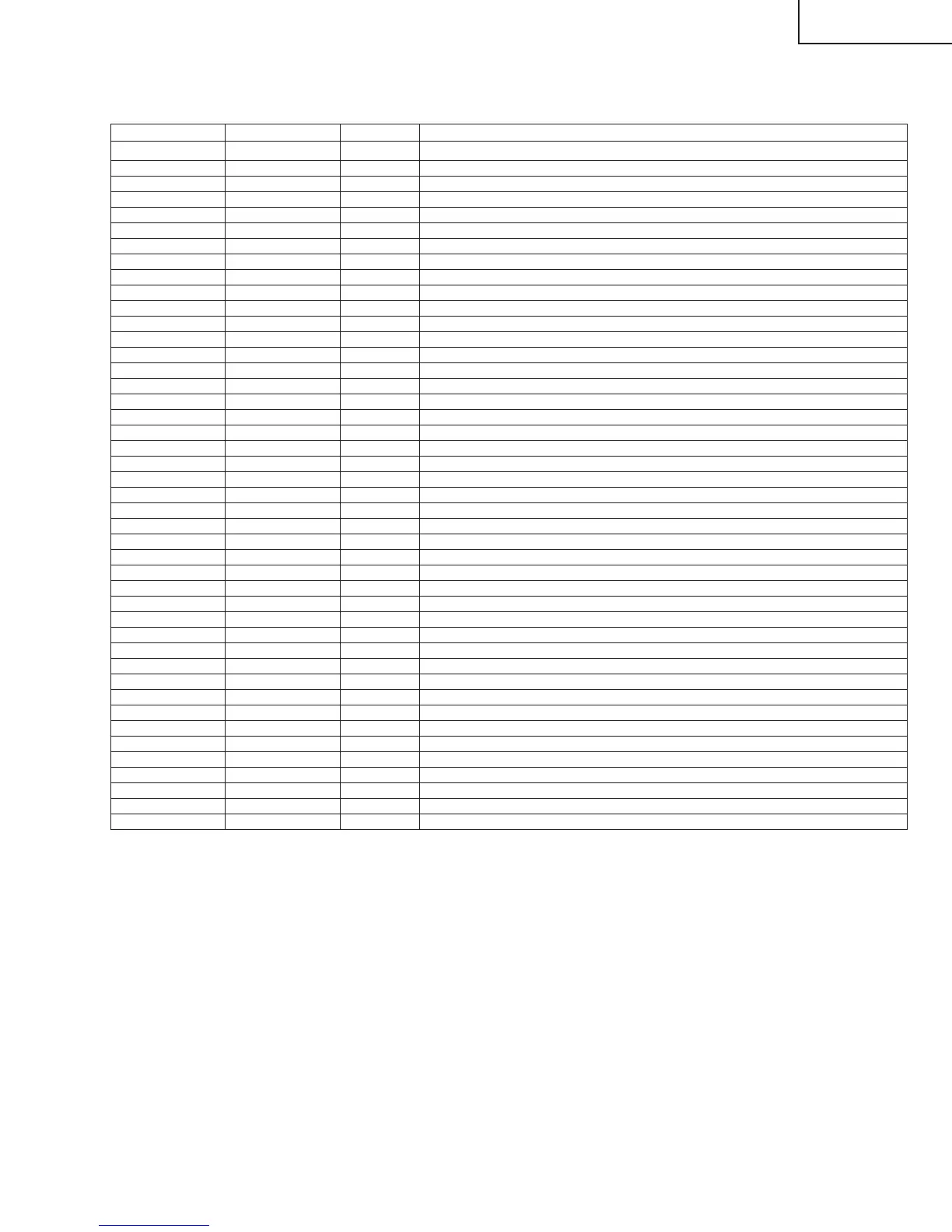

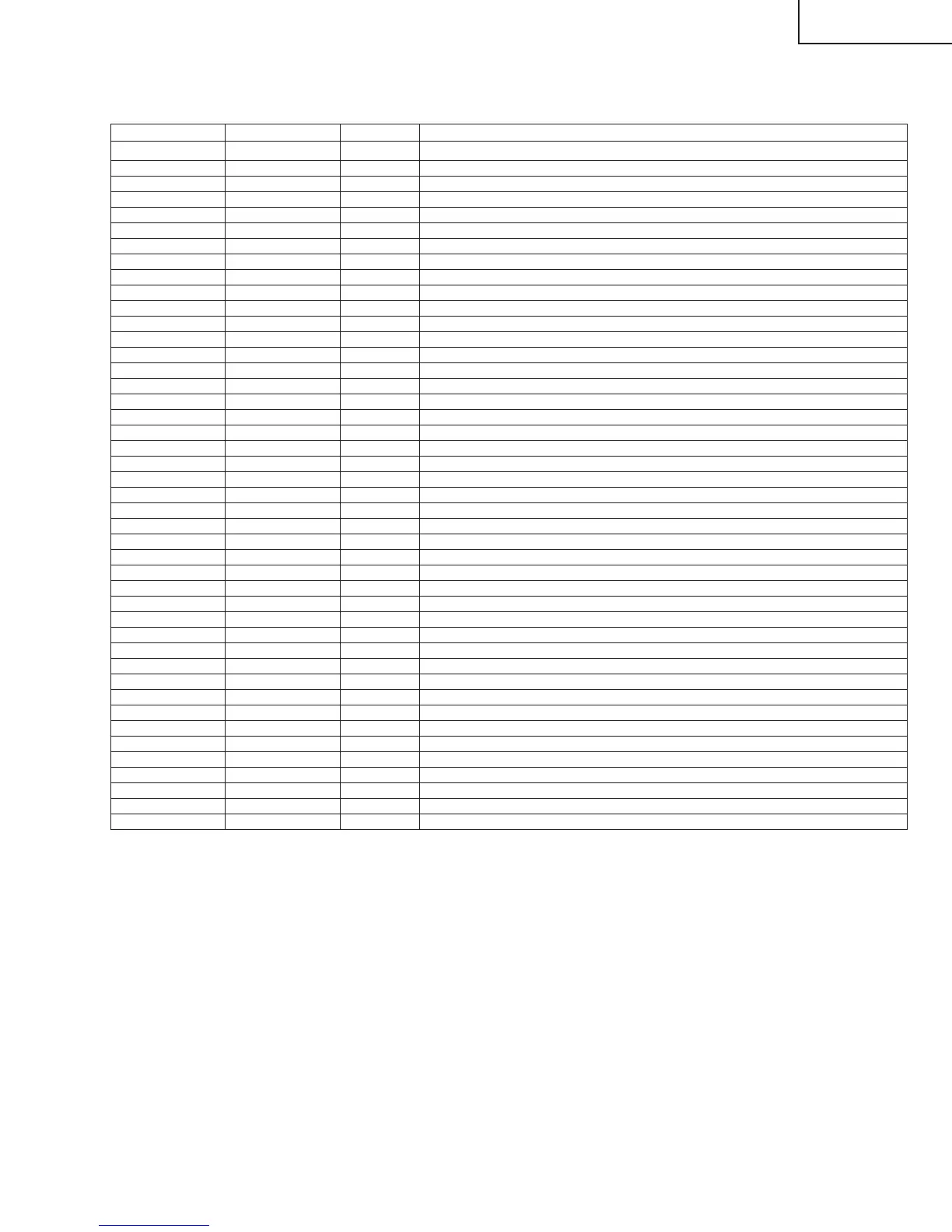

Pin No. Pin Name Type Description

1 NC –– Non-connection

2 SP_CP2 I Input of clamp signal from synchronous separation IC (for 15K system)

3 SP_VD I Input of vertical synchronization signal from synchronous separation IC

4 GND –– GND

5 SP_HD I Input of horizontal synchronization signal from synchronous separation IC

6 VD3 O Output of vertical synchronization signal to synchronous separation IC

7 HD3 O Output of horizontal synchronization signal to synchronous separation IC

8 SP_CP1 I Input of clamp signal from synchronous separation IC (normal)

9 TDI I SP data input

10 TMS I SP mode input

11 TCK I SP clock input

12 TEXT_HD O TEXT_HD output

13 US_HD I RCA/TEXT horizontal synchronization signal input

14 TEXT_VD O TEXT_VD output

15 Vcc3.3V –– TEXT_VD output

16 US_VD I RCA/TEXT vertical synchronization signal input

17 GND –– GND

18 MODEA I Mode selection signal A

19 MODEB I Mode selection signal B

20 MODEC I Mode selection signal C

21 SELA I Input of HD switching control signal for main video chroma/RCA

22 SELO I Input of control signal for TEXT synchronization signal output

23 SELC I Input of control signal for TEXT synchronization signal output

24 TDO O ISP data output

25 GND –– GND

26 Vcc3.3V –– Power supply

27 VD1 I Input of vertical synchronization signal from main video chroma IC

28 HD1 I Input of horizontal synchronization signal from main video chroma IC

29 PL_VD O Vertical synchronization signal output

30 PL_HD O Horizontal synchronization signal output

31 PL_CP O Clamp signal output

32 PL_BLK O H blank signal output

33 MODED I Mode selection signal D

34 NC –– Non-connection

35 Vcc3.3V –– Power supply

36 NC –– Non-connection

37 CC_HD O Horizontal synchronization signal for closed caption

38 ow_vblk I Auto wide V blank signal input

39 HDS O Output of horizontal synchronization signal for PC I/F unit

40 VDS O Output of vertical synchronization signal for PC I/F unit

41 HD2 I Input of horizontal synchronization signal from sub video chroma IC

42 VD2 I Input of vertical synchronization signal from sub video chroma IC

43 clk I Clock input

44 NC –– Non-connection

ËRH-iXA392WJZZ (ASSY:IC1901)

PLD (Programmable Logic Device)

» Pin mapping

Loading...

Loading...