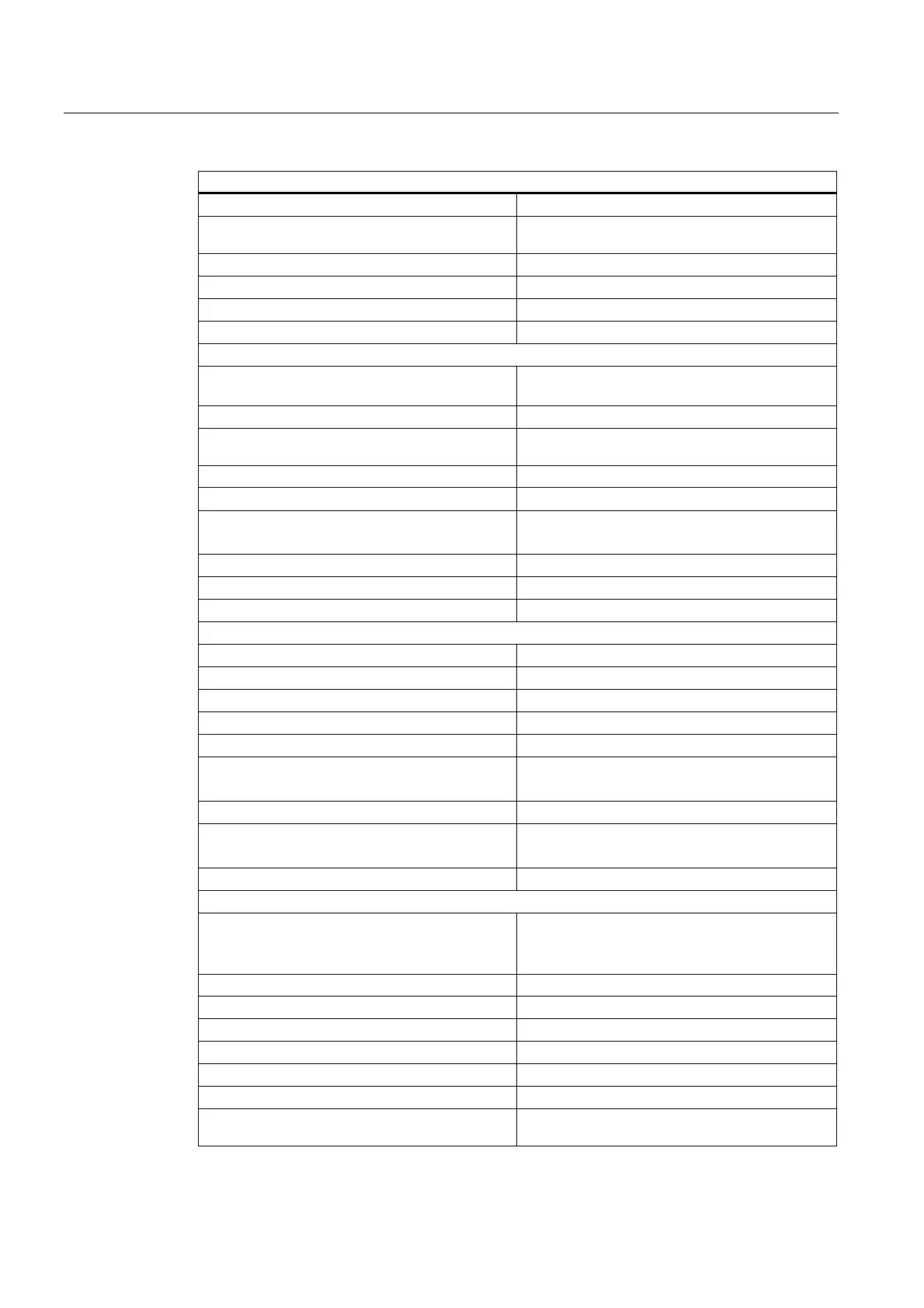

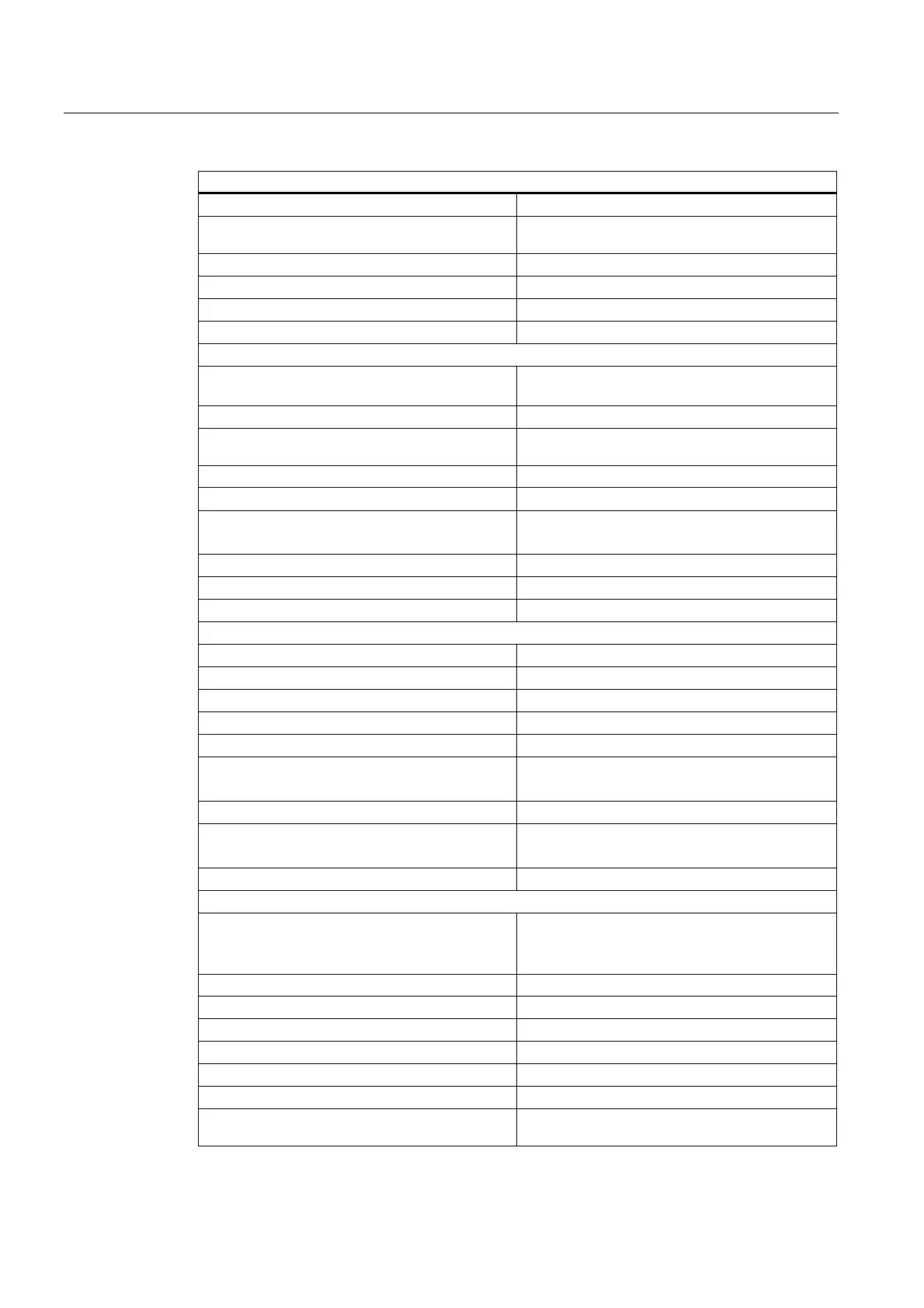

Technical specifications

10.1 Technical Specification of the CPU 414-3 PN/DP; (6ES7414-3EM05-0AB0)

S7-400 Automation System, CPU Specifications

10-2 Manual, 10/2006, 6ES7498-8AA04-8BA0

CPU and firmware version

S7 timers 2048

• Retentive address areas,

configurable

From T 0 to T 2047

• Preset

No retentive timers

• Timer range

10 ms to 9990 s

IEC timers Yes

• Type

SFB

Data areas and their retentive address areas

Total retentive data areas (including memory bits;

times; counts)

Total working and load memory (with backup

battery)

Bit memory 8 KB

• Retentive address areas,

configurable

From MB 0 to MB 8191

• Preset retentive address areas

MB 0 to MB 15

Clock flag bits 8 (1 flag byte)

Data blocks Max. 6000 (DB 0 reserved)

in the 1 to 16 000 range of numbers

• Size

Max. 64 KB

Local data (can be set) Max. 16 KB

• Preset

8 KB

Blocks

OBs See

Instruction List

• Size

Max. 64 KB

Nesting depth

• Per priority class

24

• Additionally within an error OB

1

FBs Max. 3000

in the 1 to 16 000 range of numbers

• Size

Max. 64 KB

FCs Max. 3000

in the 1 to 16 000 range of numbers

• Size

Max. 64 KB

Address areas (I/O)

Total I/O address area 8 KB / 8 KB

including diagnostics addresses for I/O interfaces,

etc.

• Distributed

MPI/DP interface 2 KB / 2 KB

DP interface 6 KB / 6 KB

PN interface 8 KB / 8 KB

Process image 8 KB / 8 KB (can be set)

• Preset

256 bytes / 256 bytes

• Number of process image

partitions

Max. 15

Loading...

Loading...