Technical specifications

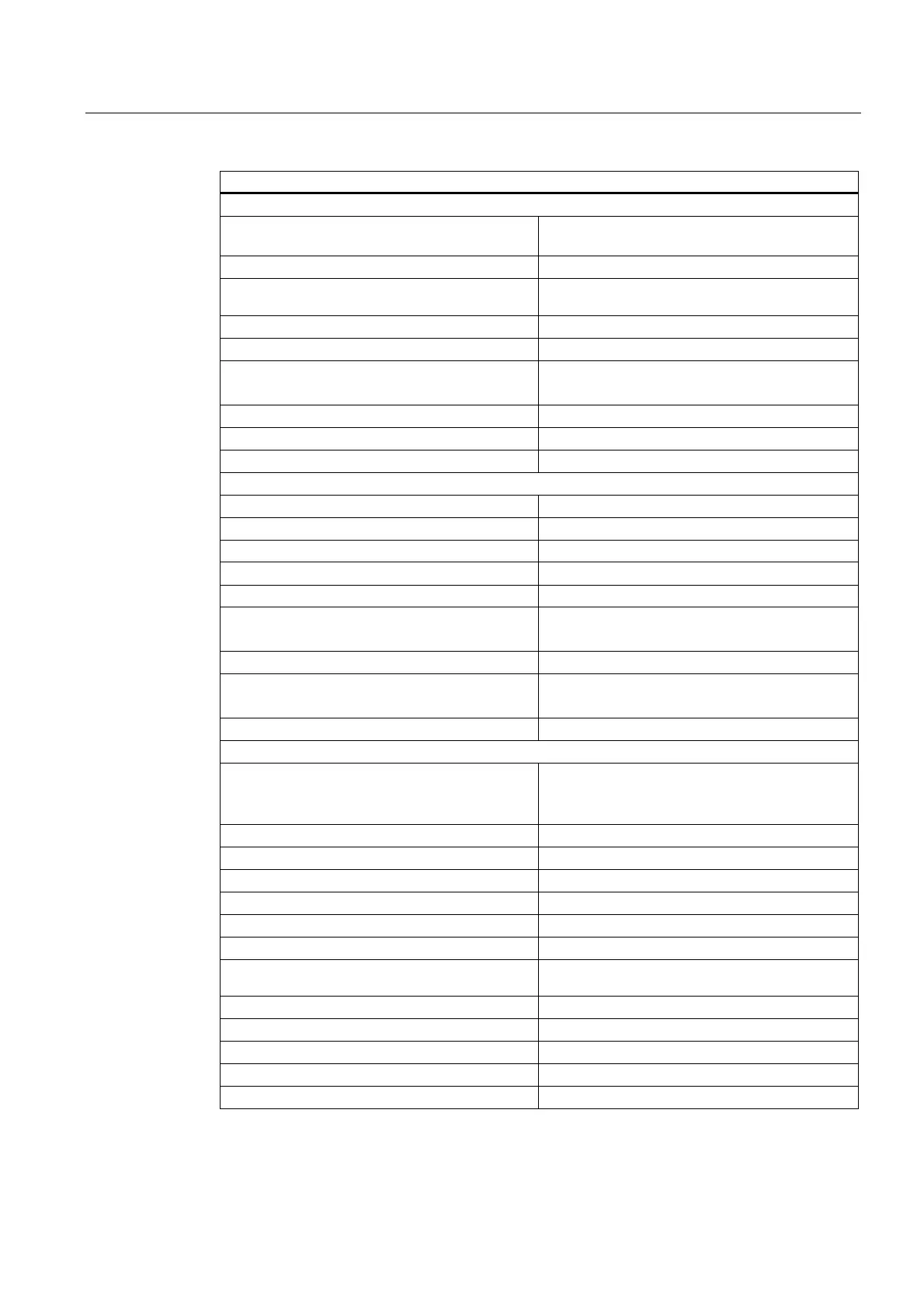

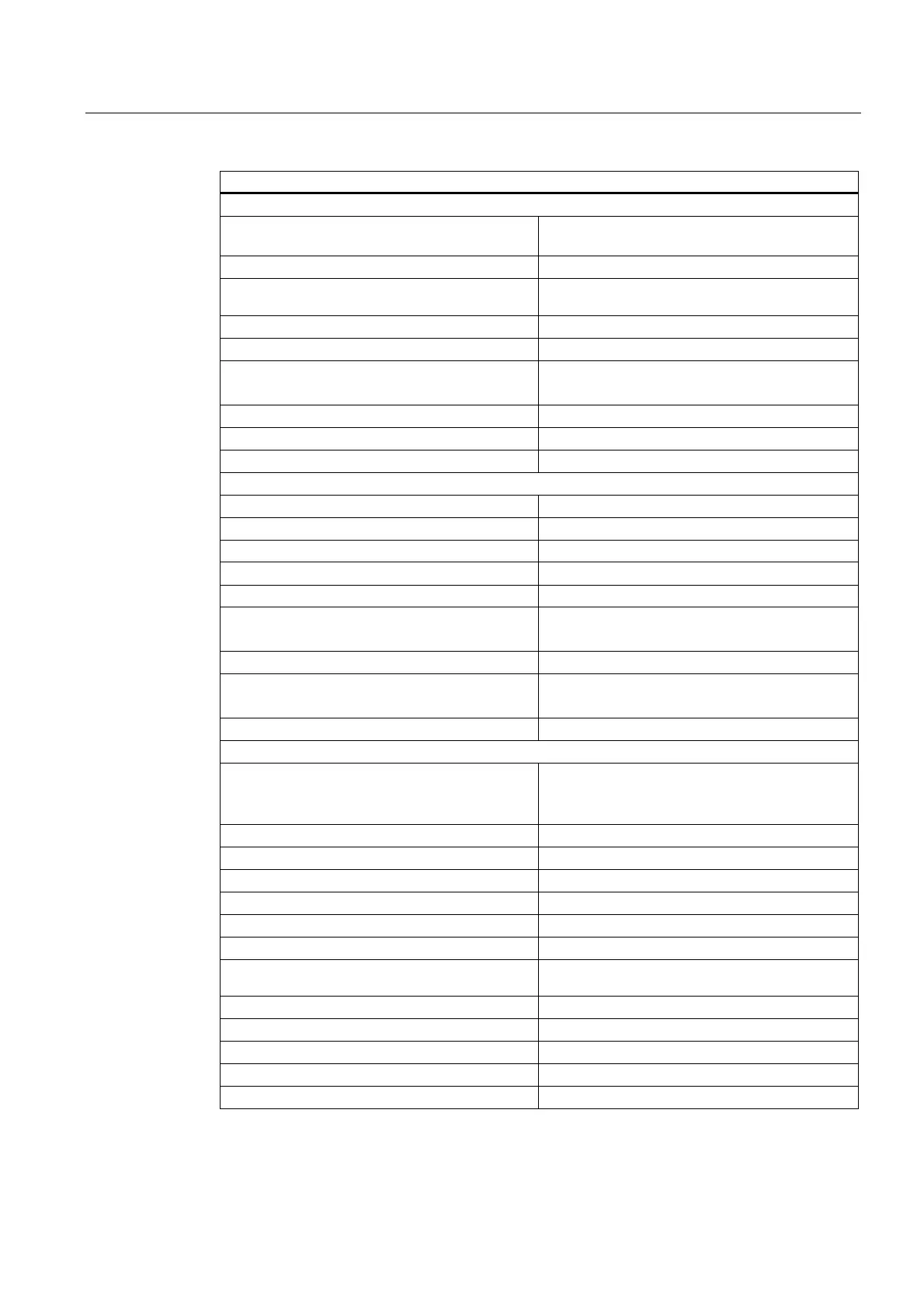

10.2 Technical Specification of the CPU 416-3 PN/DP; (6ES7416-3ER05-0AB0)

S7-400 Automation System, CPU Specifications

Manual, 10/2006, 6ES7498-8AA04-8BA0

10-17

CPU and firmware version

Data areas and their retentive address areas

Total retentive data area (including memory

markers, timers, counters)

Total working and load memory (with backup

battery)

Bit memory 16 KB

• Retentive address areas,

configurable

MB 0 to MB 16383

• Preset retentive address areas

MB 0 to MB 15

Clock flag bits 8 (1 flag byte)

Data blocks Max. 10000 (DB 0 reserved)

in the 1 to 16 000 range of numbers

• Size

Max. 64 KB

Local data (can be set) Max. 32 KB

• Preset

16 KB

Blocks

OBs See

Instruction List

• Size

Max. 64 KB

Nesting depth

• Per priority class

24

• Additionally within an error OB

2

FBs Max. 5000

in the 1 to 16 000 range of numbers

• Size

Max. 64 KB

FCs Max. 5000

in the 1 to 16 000 range of numbers

• Size

Max. 64 KB

Address areas (I/O)

Total I/O address area 16 KB / 16 KB

including diagnostics addresses for I/O interfaces,

etc.

• Distributed

MPI/DP interface 2 KB / 2 KB

DP interface 8 KB / 8 KB

PN interface 8 KB / 8 KB

Process image 16 KB / 16 KB (can be set)

• Preset

512 bytes / 512 bytes

• Number of process image

partitions

Max. 15

• Consistent data

Max. 244 bytes

Digital channels Max. 131072 / Max. 131072

• Centralized

Max. 131072 / Max. 131072

Analog channels Max. 8192 / Max. 8192

• Centralized

Max. 8192 / Max. 8192

Loading...

Loading...