HCD-HDX285/HDX287WC/HDX585/HDX587WC/HDX589W/HDX685/HDX686W

75

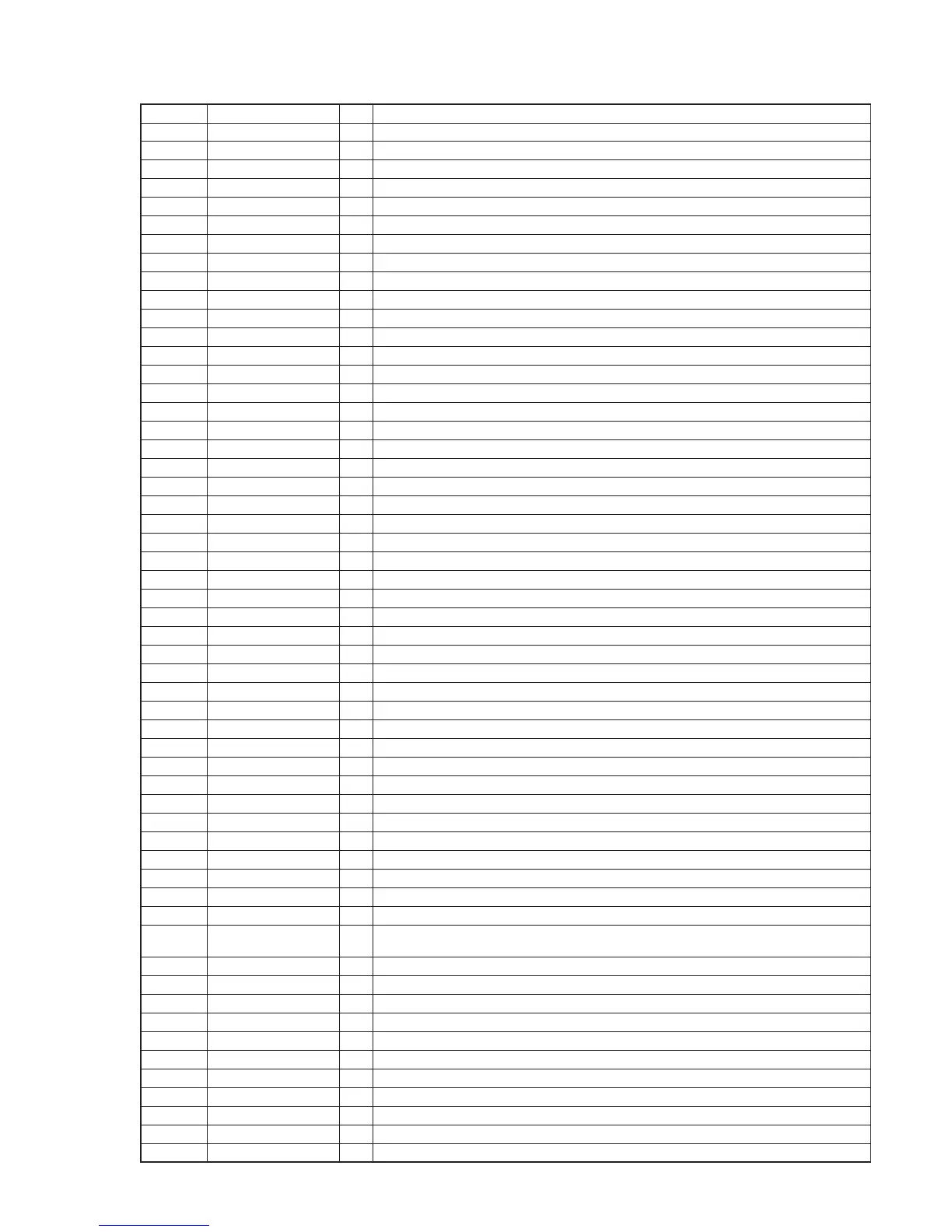

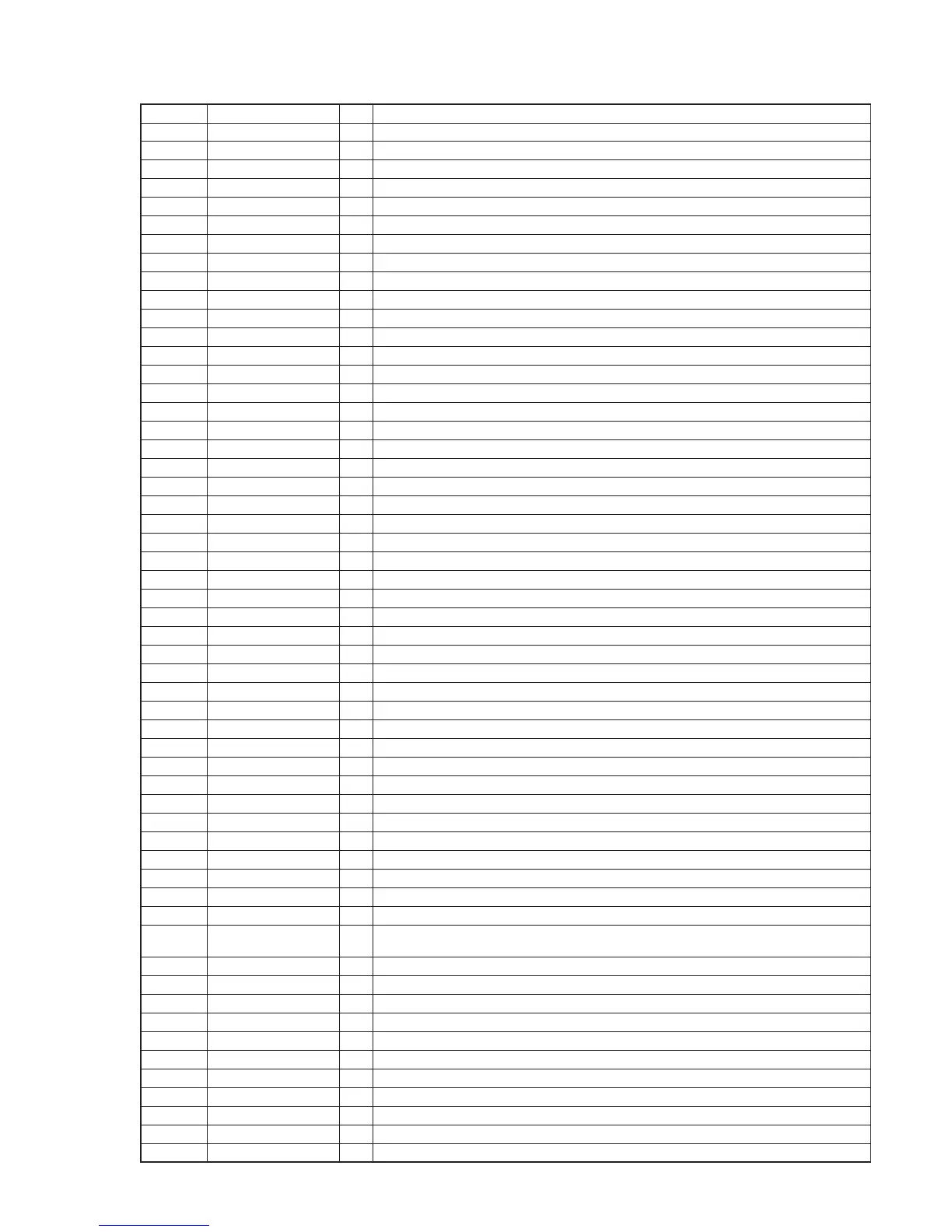

Pin No. Pin Name I/O Description

147 CKE O Clock enable signal output to the SD-RAM

148 DVSS - Ground terminal

149 to 155 RA11, RA9 to RA4 O Address signal output to the SD-RAM

156 DVDD3 - Power supply terminal (+3.3V)

157 MUTE123 O Muting signal output to the coil/motor driver (for focus/tracking coil and sled motor)

158 MUTE O Muting signal output to the coil/motor driver (for spindle motor)

159 DDC_DA I/O Two-way data bus with the HDMI OUT connector

160 DVDD18 - Power supply terminal (+1.8V)

161 DDC_CLK O Serial data transfer clock signal output to the HDMI OUT connector

162 HTPLG I HDMI hot plug detection signal input terminal

163 AGND3 - Ground terminal

164 EXT_RES I External resistor connecting terminal

165, 166 AVDD3 - Power supply terminal (+3.3V)

167 EXT_CAP I External capacitor connecting terminal

168, 169 AGND3, AGND18 - Ground terminal

170 TXCN O TMDS clock signal (negative) output to the HDMI OUT connector

171 TXCP O TMDS clock signal (positive) output to the HDMI OUT connector

172 AVDD18 - Power supply terminal (+1.8V)

173 TX0N O TMDS data (negative) output to the HDMI OUT connector

174 TX0P O TMDS data (positive) output to the HDMI OUT connector

175 AGND18 - Ground terminal

176 TX1N O TMDS data (negative) output to the HDMI OUT connector

177 TX1P O TMDS data (positive) output to the HDMI OUT connector

178 AVDD18 - Power supply terminal (+1.8V)

179 TX2N O TMDS data (negative) output to the HDMI OUT connector

180 TX2P O TMDS data (positive) output to the HDMI OUT connector

181 AGND18 - Ground terminal

182 R/Cr/Pr O Component video (Pr/Cr) signal output to the video amplifi er

183 B/Cb/Pb O Component video (Pb/Cb) signal output to the video amplifi er

184 DACVSSA - Ground terminal

185 Y/G O Component video (Y) signal output to the video amplifi er

186 DACVDDA - Power supply terminal (+3.3V)

187 CVBS O Composite video signal output to the video amplifi er Not used

188 DACVSSB - Ground terminal

189 C O Chroma signal output to the video amplifi er

190 DACVDDB - Power supply terminal (+3.3V)

191 Y O Y signal output to the video amplifi er

192 DACVSSC - Ground terminal

193 FS I Full scale adjustment terminal

194 VREF I Bandgap reference voltage terminal

195 DACVDDC - Power supply terminal (+3.3V)

196 VBUS_OE O VBUS control signal output terminal Not used

197 VBUS_OC I VBUS over current detection signal input terminal Not used

198 DIR_XSTATE I

Clock change status detection signal input from the digital audio interface receiver

"L": change

199 SPMCK I Master clock signal input from the digital audio interface receiver

200 SPBCK I Bit clock signal input from the digital audio interface receiver

201 SPLRCK I L/R sampling clock signal input from the digital audio interface receiver

202 ADIN(SPDATA) I Audio data input from the digital audio interface receiver

203 ACLK O Master clock signal output to the stream processor

204 ABCK O Bit clock signal output to the stream processor

205 ALRCK O L/R sampling clock signal output to the stream processor

206 MC_DATA(ADIN) I Audio data input from the A/D converter

207 DVDD3 - Power supply terminal (+3.3V)

208 MIC I Karaoke microphone detection signal input terminal Not used

209 WIDE O Normal/squeeze selection signal output terminal Not used

Loading...

Loading...