67

STR-DG910

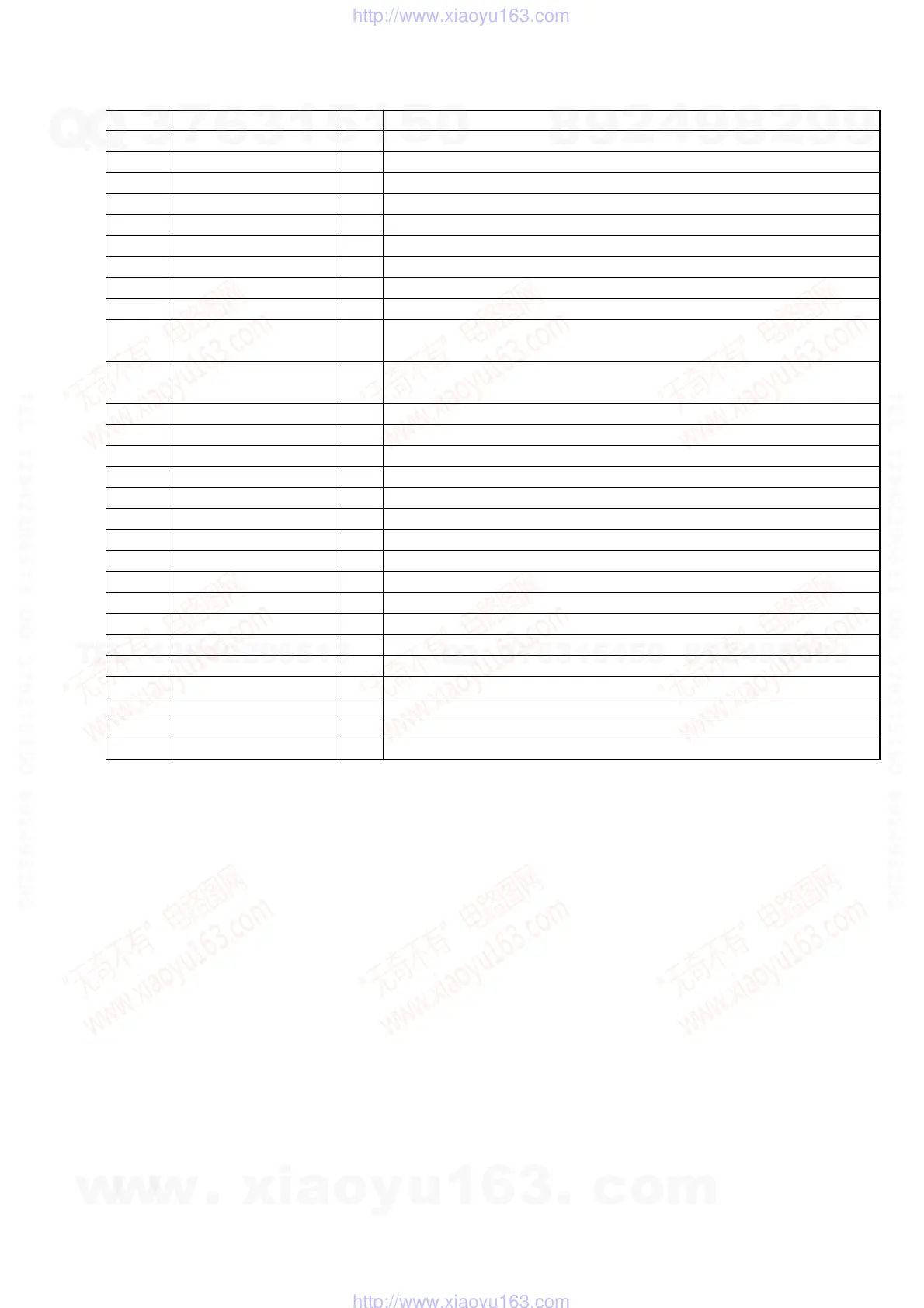

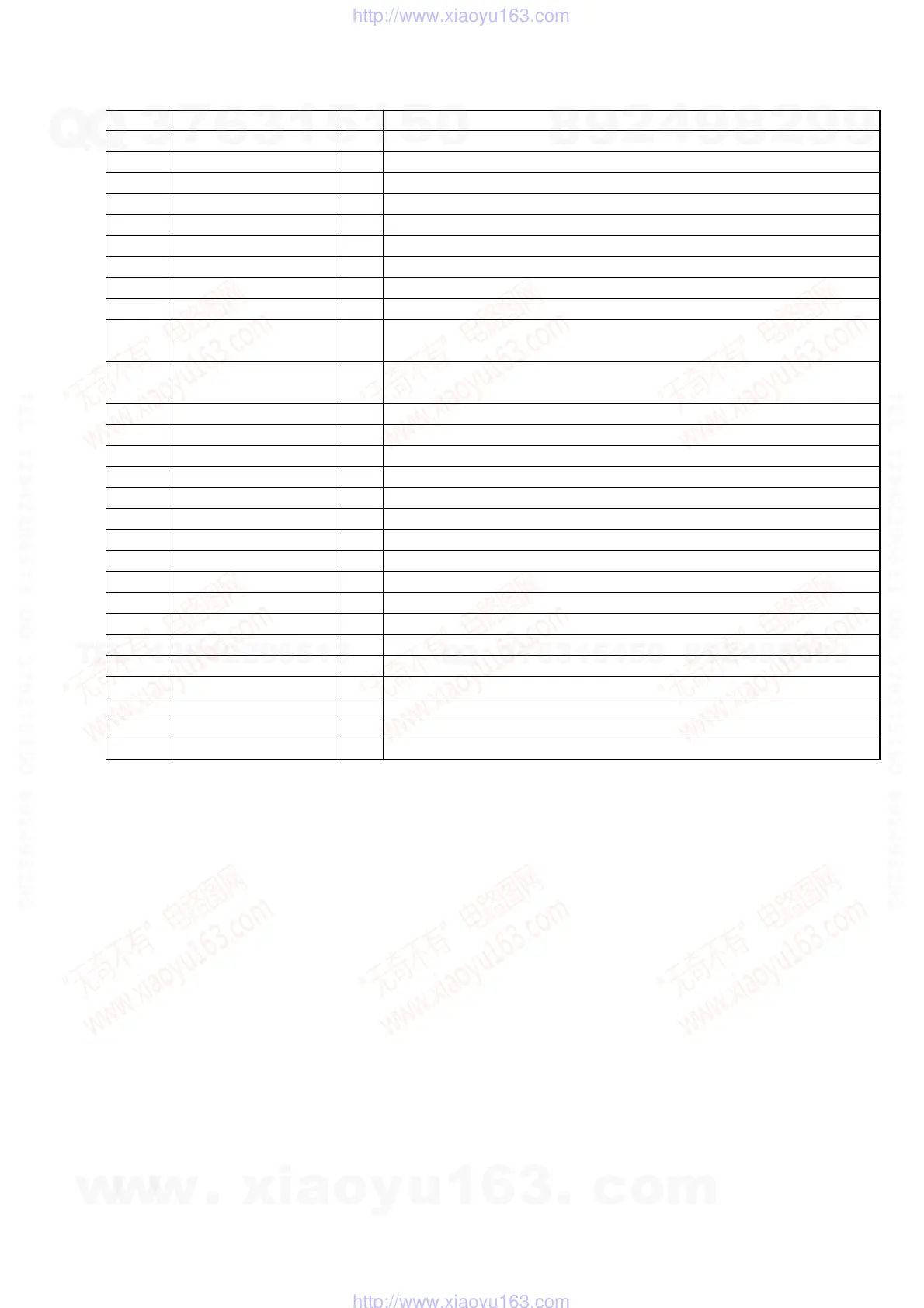

Pin No. Pin Name I/O Pin Description

117 GND — Ground

118 VDDINT — Power supply terminal (+1.2 V)

119 GND — Ground

120 VDDINT — Power supply terminal (+1.2 V)

121 XRESET I System reset signal input from main system controller.

122 XSPIDS I Serial data latch pulse signal input from main system controller.

123 GND — Ground

124 VDDINT — Power supply terminal (+1.2 V)

125 SPICLK I/O Serial data transfer clock signal input/output with flash memory.

126 MISO I/O

When DSP is master: Serial data input from flash memory.

When DSP is slave: Serial data output for main system controller.

127 MOSI I/O

When DSP is master: Serial data output for flash memory.

When DSP is slave: Serial data input from main system controller.

128 GND — Ground

129 VDDINT — Power supply terminal (+1.2 V)

130 VDDEXT — Power supply terminal (+3.3 V)

131 AVDD — Power supply terminal (+1.2 V)

132 AVSS — Ground

133 GND — Ground

134 CLKOUT — Not used. (Open)

135 XEMU — Not used. (Open)

136 TDO — Not used. (Open)

137 TDI — Not used. (Fixed at L in this set)

138 CTRST — Not used. (Fixed at L in this set)

139 TCK — Not used. (Fixed at L in this set)

140 TMS — Not used. (Fixed at L in this set)

141 GND — Ground

142 CLKIN I System clock input (25 MHz)

143 XTAL O System clock output (25 MHz)

144 VDDEXT — Power supply terminal (+3.3 V)

w

w

w

.

x

i

a

o

y

u

1

6

3

.

c

o

m

Q

Q

3

7

6

3

1

5

1

5

0

9

9

2

8

9

4

2

9

8

T

E

L

1

3

9

4

2

2

9

6

5

1

3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299

http://www.xiaoyu163.com

http://www.xiaoyu163.com

Loading...

Loading...