RM0440 Rev 4 2077/2126

RM0440 USB Type-C™ / USB Power Delivery interface (UCPD)

2079

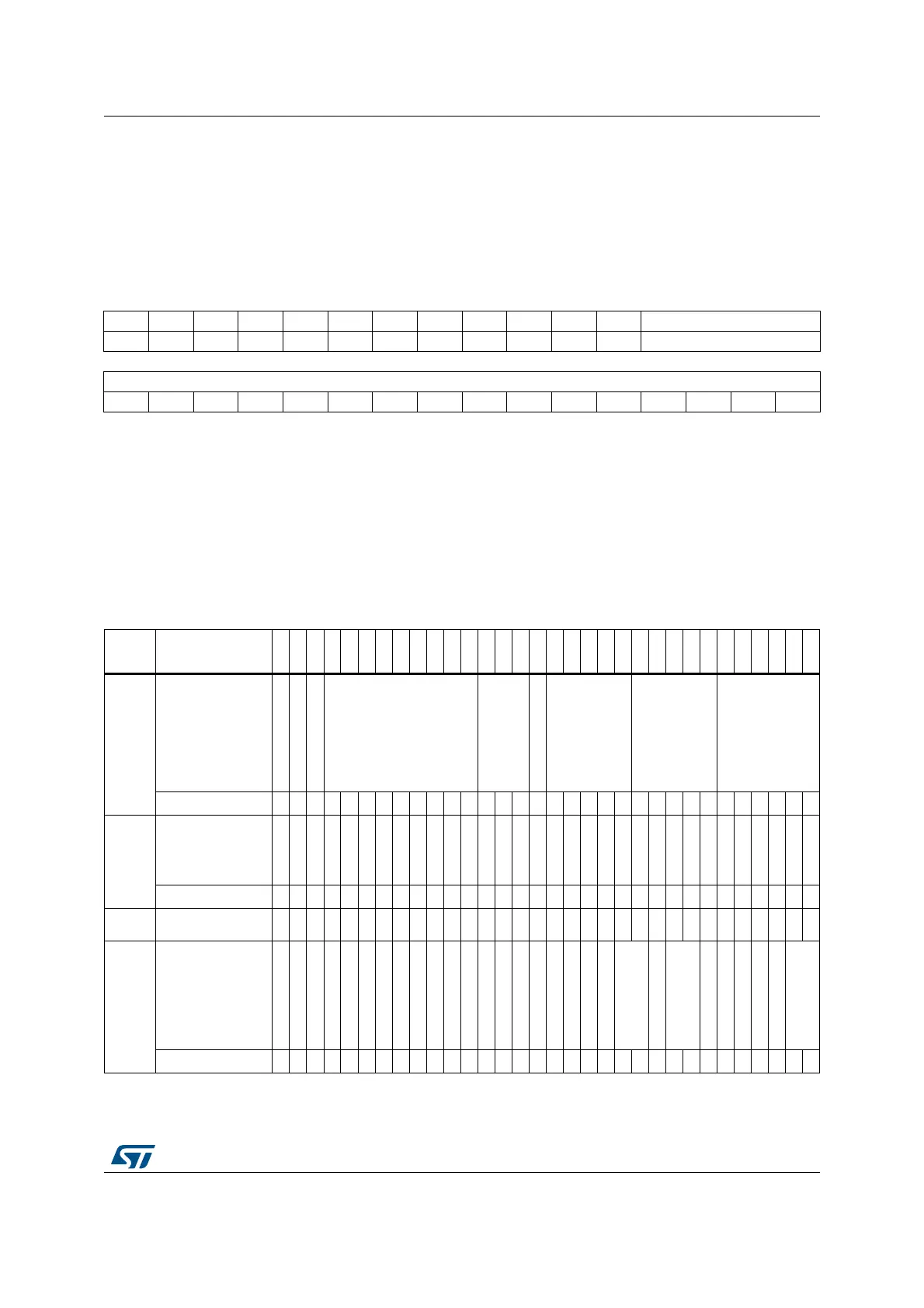

46.7.14 UCPD Rx ordered set extension register 2

(UCPD_RX_ORDEXTR2)

Address offset: 0x038

Reset value: 0x0000 0000

Writing to this register is only effective when the peripheral is disabled (UCPDEN = 0).

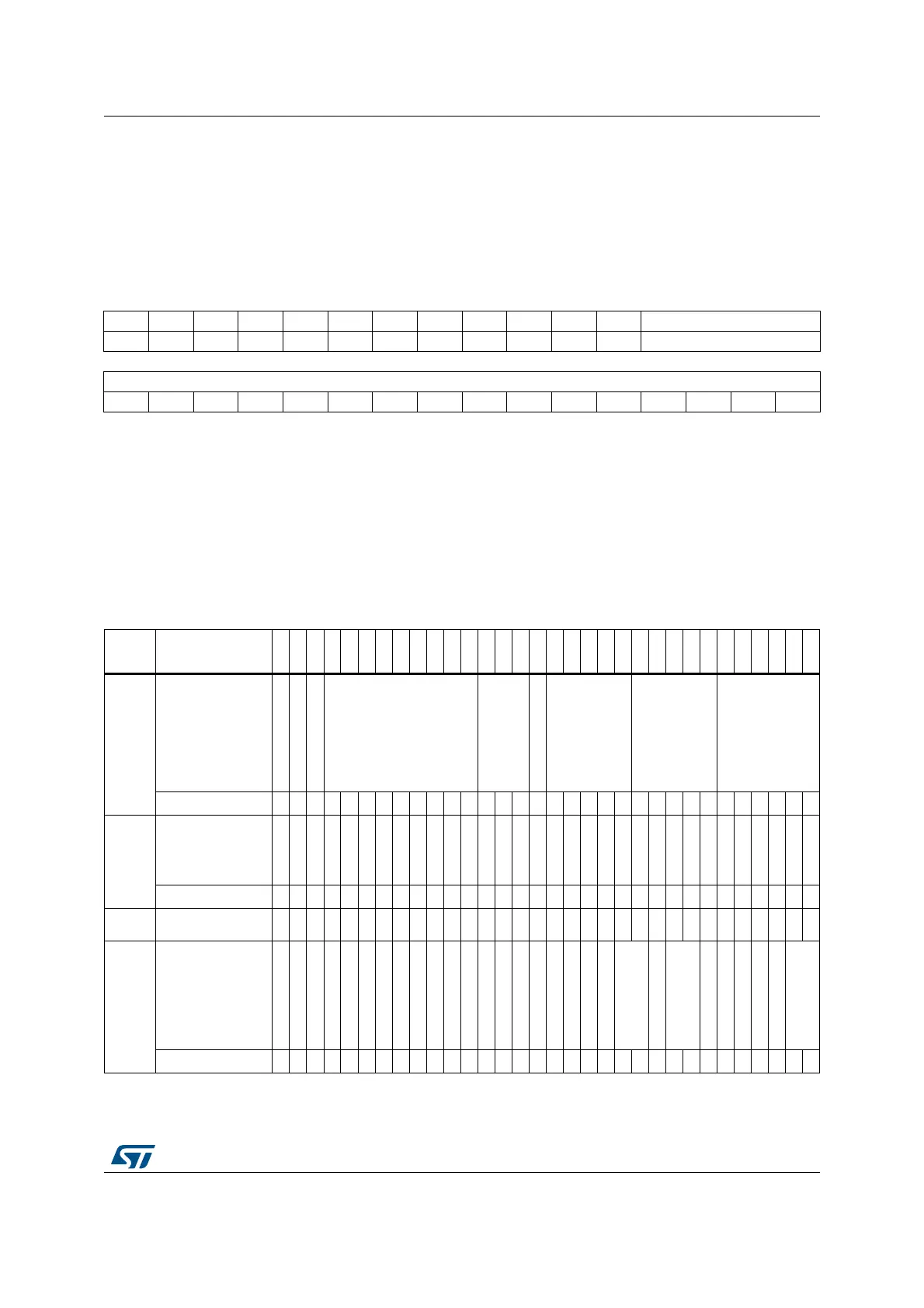

46.7.15 UCPD register map

The following table gives the UCPD register map and reset values.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. RXSOPX2[19:16]

rw

1514131211109876543210

RXSOPX2[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:20 Reserved, must be kept at reset value.

Bits 19:0 RXSOPX2[19:0]: Ordered set 2 received

The bitfield contains a full 20-bit sequence received, consisting of four K-codes, each of five

bits. The bit 0 (bit 0 of K-code1) is receive first, the bit 19 (bit 4 of K-code4) last.

Table 429. UCPD register map and reset values

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0x000

UCPD_CFG1

UCPDEN

RXDMAEN

TXDMAEN

RXORDSETEN[8:0]

PSC_USBPDCLK[2:0]

Res.

TRANSWIN[4:0]

IFRGAP[4:0]

HBITCLKDIV[5:0]

Reset value 000000000000000 0000000000000000

0x004

UCPD_CFG2

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

WUPEN

FORCECLK

RXFILT2N3

RXFILTDIS

Reset value 0000

0x008 Reserved

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

0x00C

UCPD_CR

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

CC2TCDIS

CC1TCDIS

Res.

RDCH

FRSTX

FRSRXEN

Res.

Res.

Res.

Res.

CCENABLE[1:0]

ANAMODE

ANASUBMODE[1:0]

PHYCCSEL

PHYRXEN

RXMODE

TXHRST

TXSEND

TXMODE[1:0]

Reset value 000000 000000000000000

Loading...

Loading...