RM0440 Rev 4 877/2126

RM0440 High-resolution timer (HRTIM)

1083

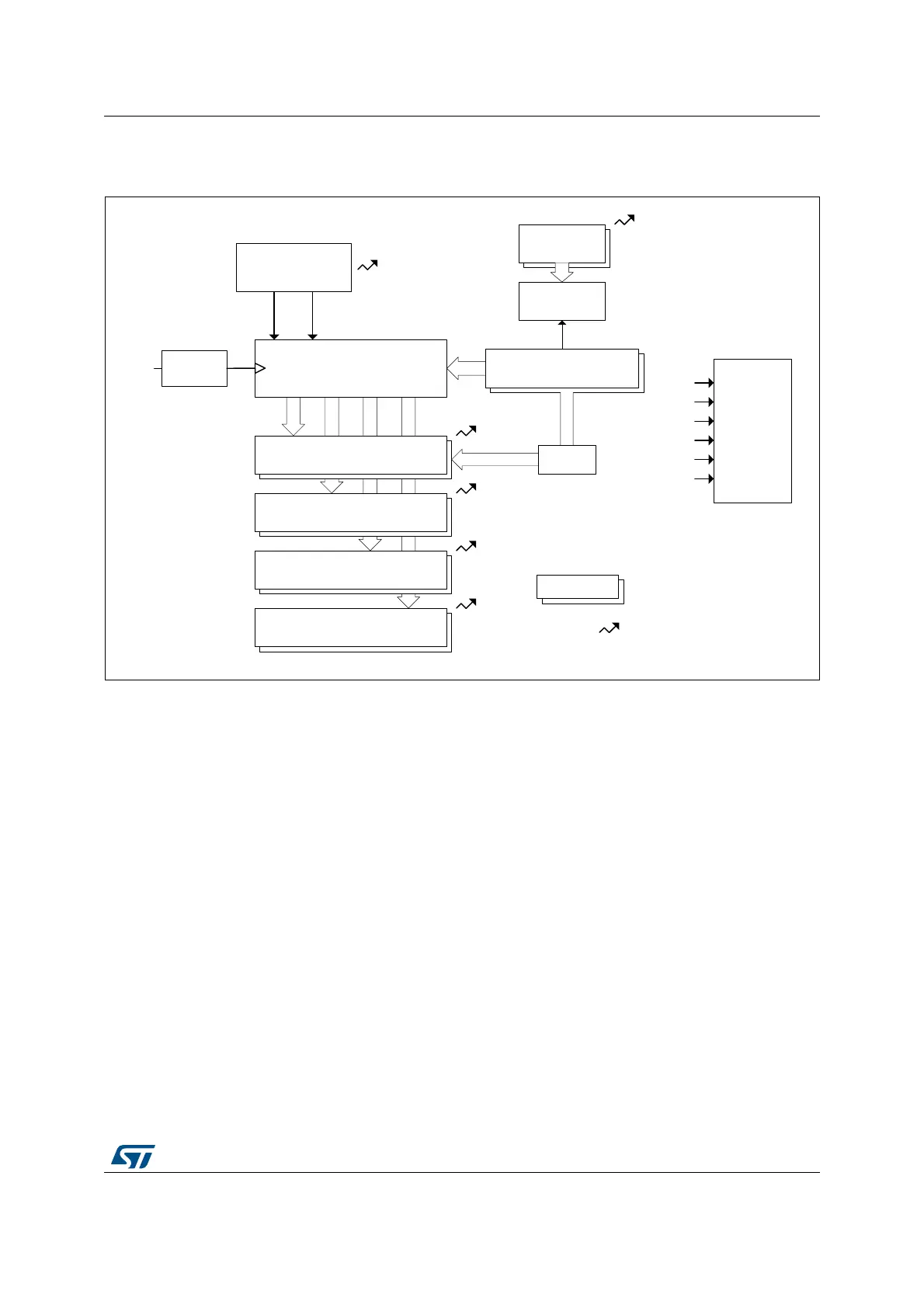

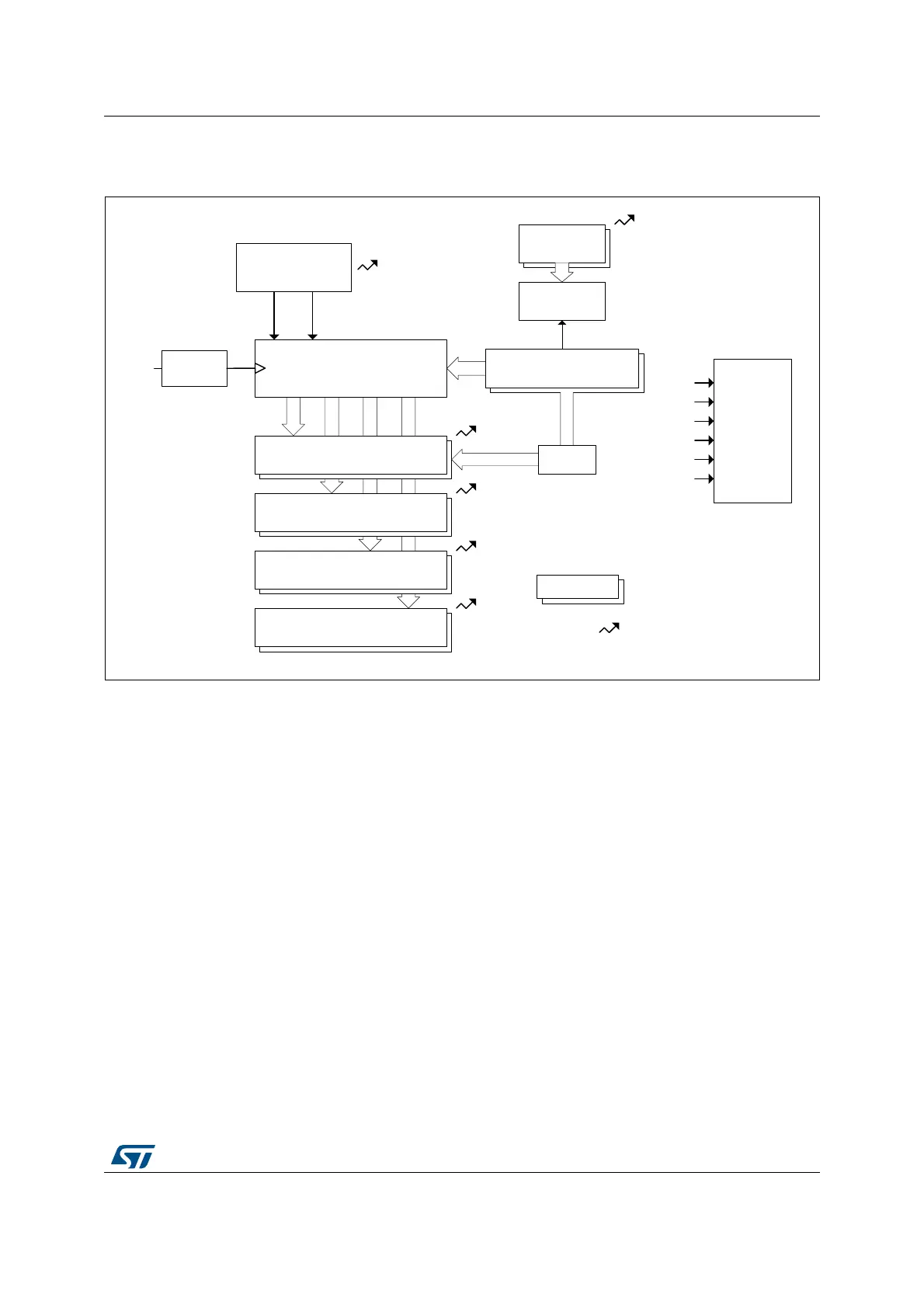

Figure 204 provides an overview of the master timer.

Figure 204. Master timer overview

The master timer is based on the very same architecture as the timing units, with the

following differences:

• It does not have outputs associated with, nor output related control

• It does not have its own crossbar unit, nor push-pull or deadtime mode

• It can only be reset by the external synchronization circuitry

• It does not have a capture unit, nor the auto-delayed mode

• It does not include external event blanking and windowing circuitry

• It has a limited set of interrupt / DMA requests: compare 1..4, repetition, register update

and external synchronization event.

The master timer control register includes all the timer enable bits, for the master and timer

A..F timing units. This allows to have all timer synchronously started with a single write

access.

It also handles the external synchronization for the whole HRTIM timer (see

Section 27.3.19: Synchronizing the HRTIM with other timers or HRTIM instances), with both

MCU internal and external (inputs/outputs) resources.

Master timer control registers are mapped with the same offset as the timing units’ registers.

MS32276V2

Counter

Prescaler

Compare 2

Compare 1

Compare 3

Compare 4

Period

Counter

Half

Repetition

Register

CMP1

CMP2

CMP3

CMP4

REP

SYNC

Denotes a register with preload

Interrupt / DMA request

f

HRTIM

To Timer

A..F

crossbars

REP

CMP1

CMP2

CMP3

CMP4

SYNC

ck

Start Reset

External

Synchronization

Unit

Loading...

Loading...