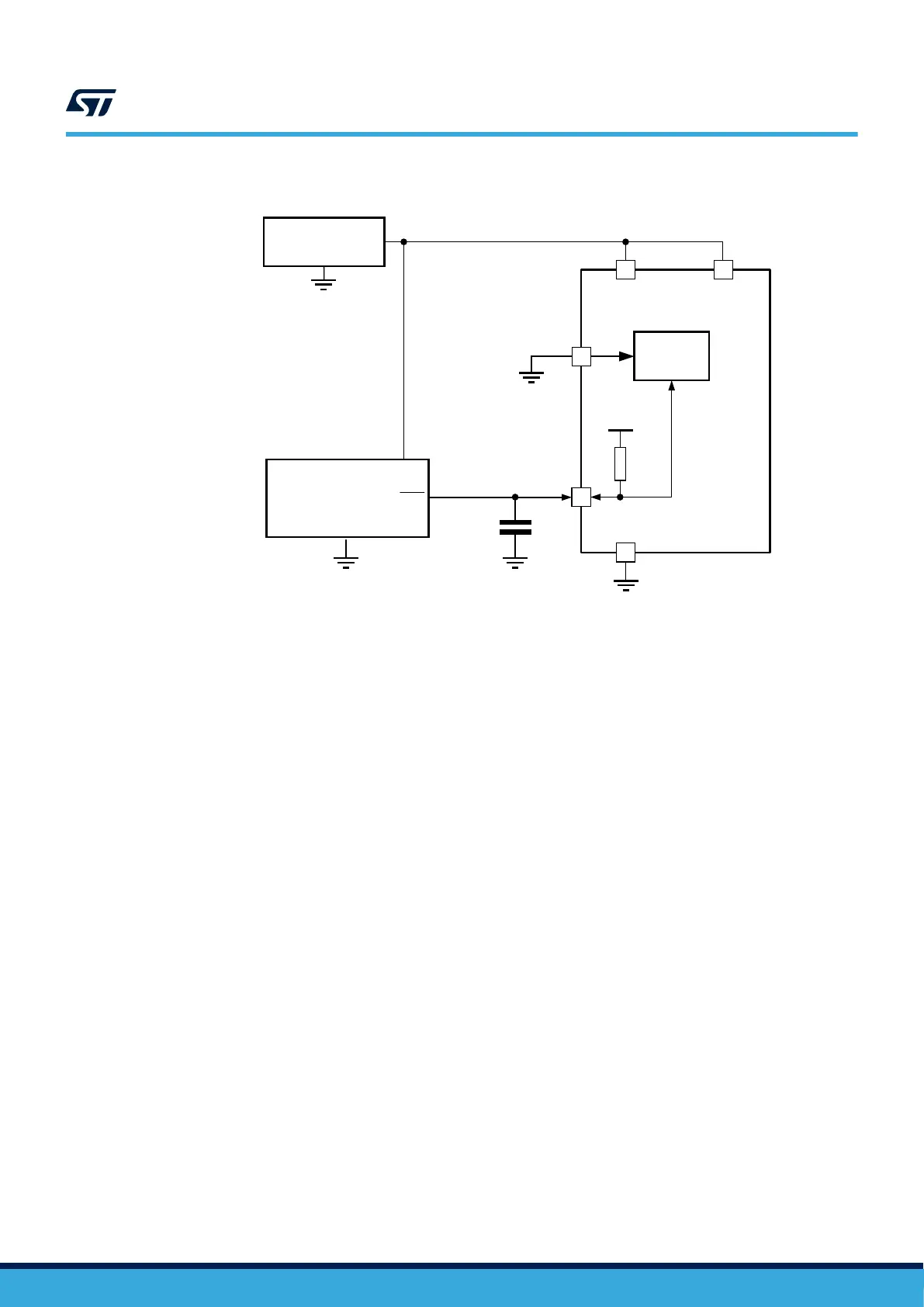

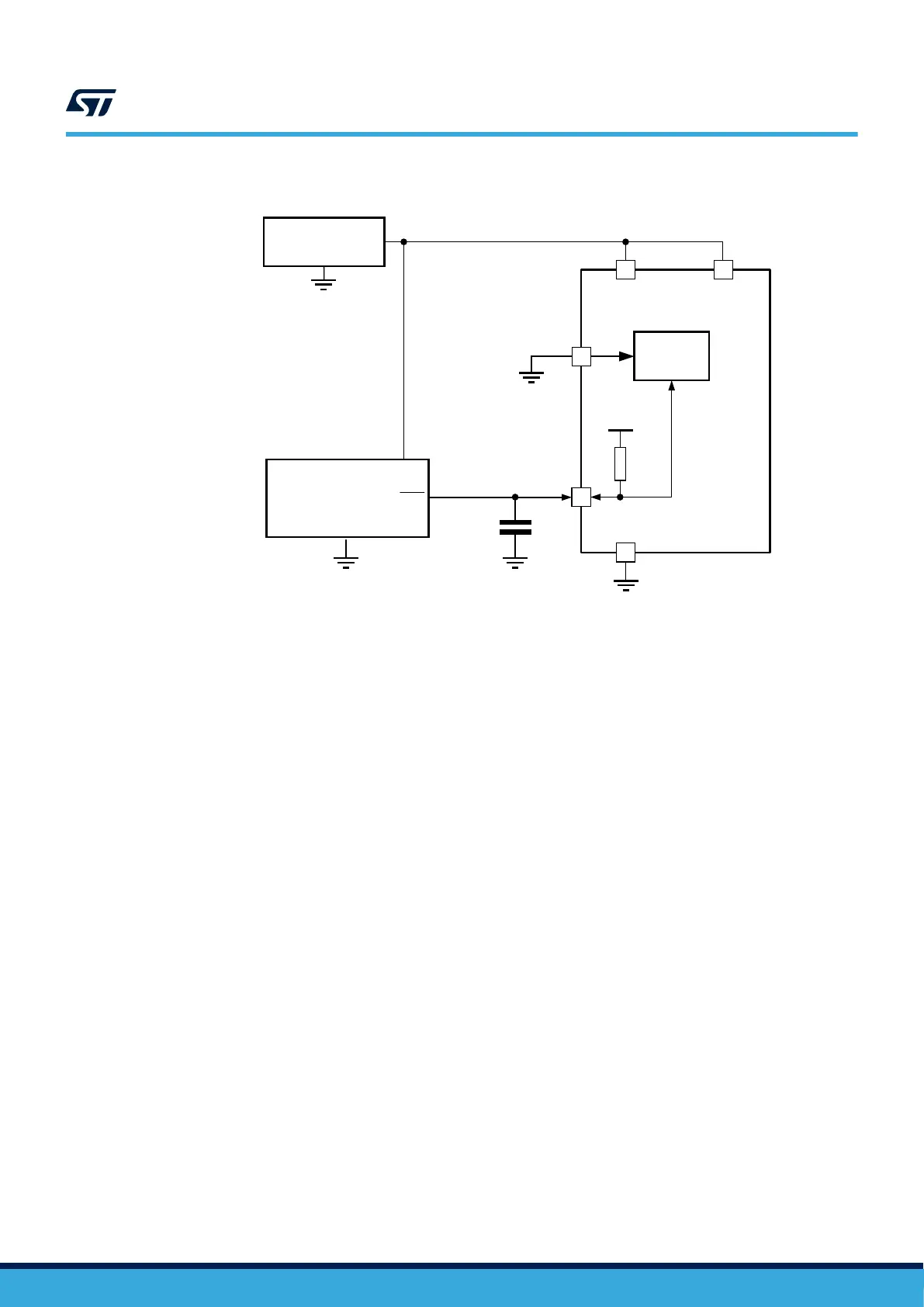

Figure 8. Power supply supervisor interconnection with internal reset OFF

STM32H7

PDR_ON

Reset

controller

Voltage regulator

1.8 V typ. (1.62 V min.)

NRST

40 kΩ

0.1 µF

OUT

STM1061N16

V

DD

V

BAT

V

DD

V

SS

/V

SSA

Voltage supervisor

Active-low and open-drain

output

The supply ranges which never go below the 1.71 V are managed more effectively using the internal circuitry (no

additional components are needed, thanks to the fully embedded reset controller).

When the embedded power supply supervisor is off, the following integrated features are no longer supported:

• The brown out reset (BOR) circuitry must be disabled

• The embedded programmable voltage detector (PVD) is disabled

• V

BAT

functionality is no longer available and VBAT pin must be connected to V

DD

.

2.2.2 Brownout reset (BOR)

If enabled through the option bytes, the BOR keeps the system under reset until the V

DD

supply voltage reaches

the selected V

BOR

threshold (also selected through option bytes, see the reference manual STM32H723/733,

STM32H725/735 and STM32H730 advanced Arm

®

-based 32-bit MCUs (RM0468))

Three BOR levels are possible (2.1 V, 2.4 V, 2.7 V) (see the STM32H72x and STM32H73x datasheets for the

electrical characteristics)

2.2.3 Programmable voltage detector (PVD)

The PVD can be used to monitor the V

DD

power supply by comparing it to a threshold selected by the PLS[2:0]

bits in the PWR power control register (PWR_CR1).

The PVD is enabled by setting the PVDE bit.

The selectable threshold is between 1.95 V and 2.85 V (see the reference manual STM32H723/733,

STM32H725/735 and STM32H730 advanced Arm

®

-based 32-bit MCUs (RM0468)).

A PVDO flag is available in the PWR power control/status register (PWR_CSR1), to indicate if V

DD

is higher or

lower than the PVD threshold. This event is internally connected to the EXTI line16 and can generate an interrupt

if enabled through the EXTI registers.

The PVD output interrupt can be generated when V

DD

drops below the PVD threshold and/or when V

DD

rises

above the PVD threshold depending on EXTI line16 rising/falling edge configuration. As an example, the service

routine could perform emergency shutdown tasks.

AN5419

Reset and power supply supervisor

AN5419 - Rev 2

page 16/50

Loading...

Loading...