2.2 Reset and power supply supervisor

2.2.1 Power-on reset (POR)/power-down reset (PDR)

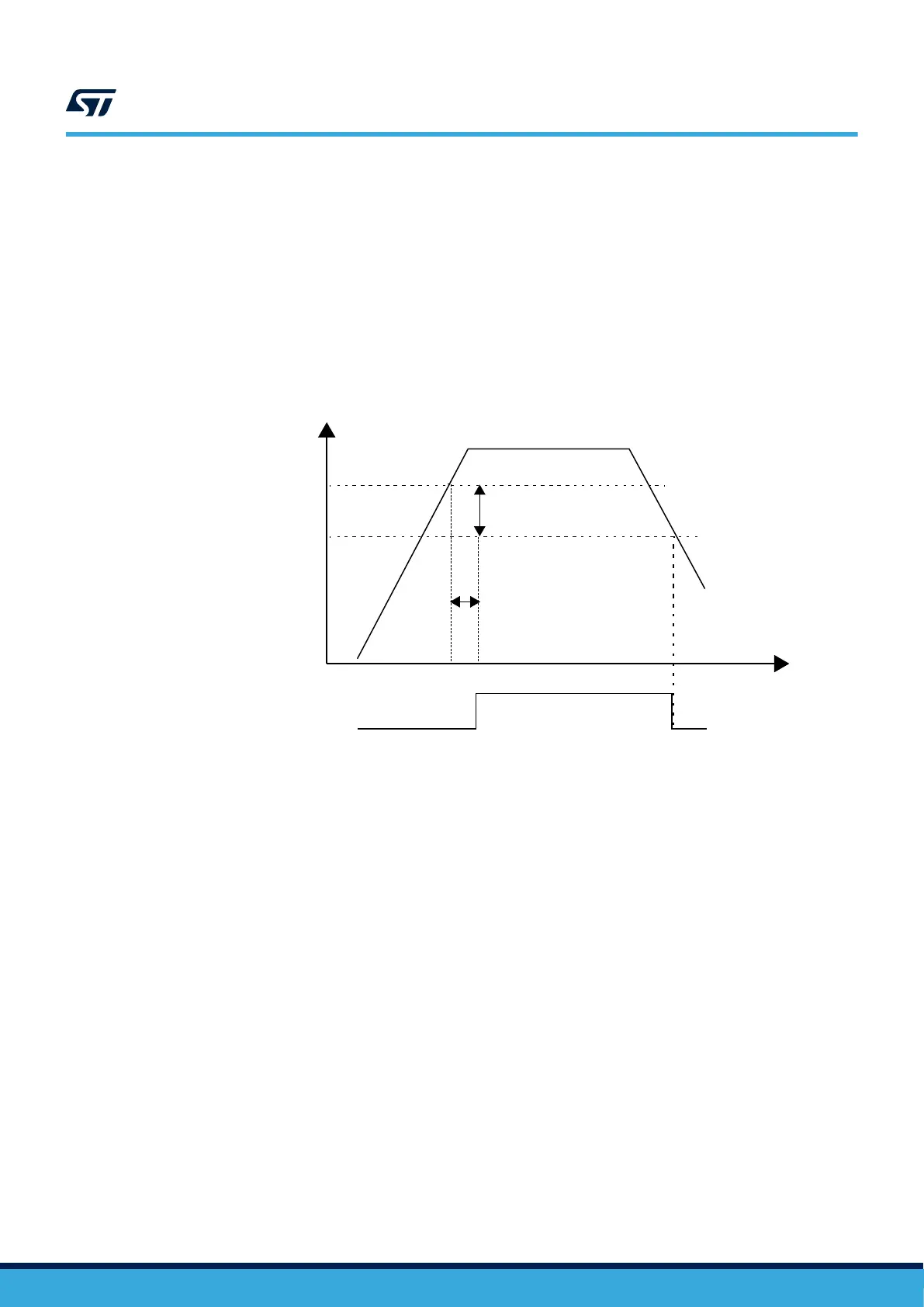

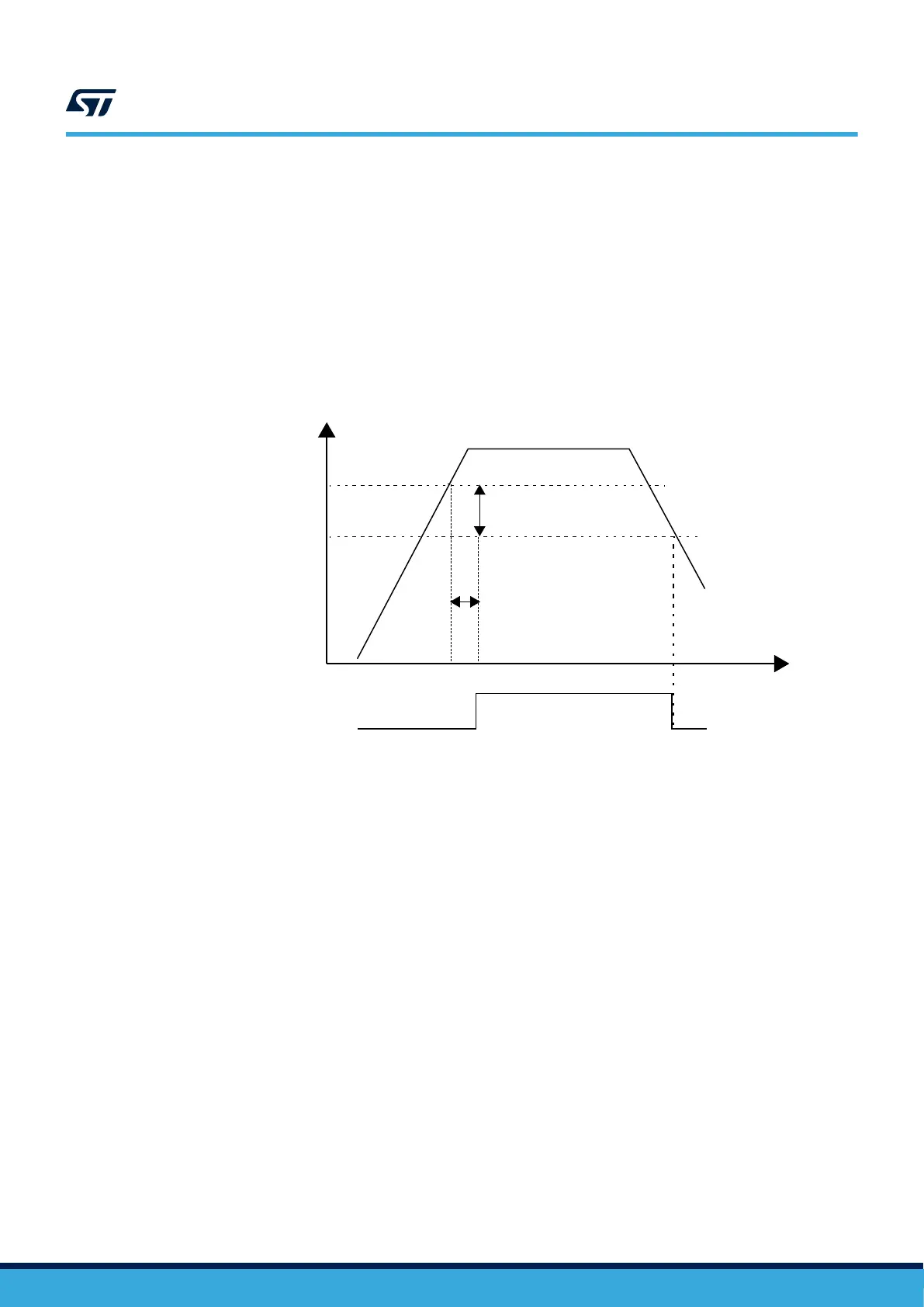

The devices have an integrated POR/PDR circuitry which ensures correct operational start-up from 1.71 V.

The device remains in reset mode while V

DD

is below a specified threshold, V

POR/PDR

, without the need for an

external reset circuit as illustrated in Figure 7. Power on reset/power down reset waveform. For more details

concerning the POR/PDR threshold, refer to the electrical characteristics of the STM32H72x and STM32H73x

datasheets.

Figure 7. Power on reset/power down reset waveform

VDD/VDDA

40 mV

hysteresis

PDR

PDR

Reset

Temporization

tRSTTEMPO

VPOR/PDR rising

edge

VPOR/PDR falling

edge

t

RSTTEMPO

is approximately 377 μs. V

POR/PDR

rising edge is 1.67 V (typical) and V

POR/PDR

falling edge is 1.62 V

(typical). Refer to the STM32H72x and STM32H73x datasheets for the actual values.

For packages embedding the PDR_ON pin, the power supply supervisor is enabled by holding PDR_ON high. On

other packages, the power supply supervisor is always enabled.

The power supply supervisor is switched off by connecting the PDR_ON pin to V

SS

, required to run the devices at

V

DD

higher than 1.71 V.

In this case, an external power supply supervisor has to monitor V

DD

and control the NRST pin.

The device must be maintained in reset mode as long as V

DD

is below 1.62 V. The implemented circuit is

illustrated in Figure 8. Power supply supervisor interconnection with internal reset OFF.

AN5419

Reset and power supply supervisor

AN5419 - Rev 2

page 15/50

Loading...

Loading...