Chapter 2: Installation

2-15

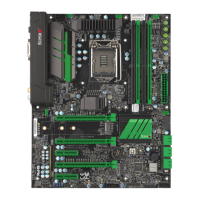

JPCIE1

JPCIE3

JPCIE6

MH12

MH10

MH11

MH13

MH14

S12

S4

MH15

JUSBA

JAUDIO1

JPCIE4

JPCIE5

JPCIE2

JUSBC

MH4

MH2

MH5

MH7

MH8

JUSBLAN1

B1

+

JBT1

10

9

2

SP1

JP2

JD1

1

15

3

1

JSD1

1

5

6

9

FAN5

FAN1

FAN4

FAN2

FAN3

JTPM1

1

2

1920

JPW1

LED20

A

C

LED17

A

C

LED19

A C

LED18

A C

LED3

LED2

A

C

A

LED1

JPW2

1

JL2

JI2C2

JI2C1

1

JSPDIF_OUT

JL1

LED4

JBR1

JLED1

1

JPAC1

1

JPL1

JWD1

JPME2

DESIGNED IN USA

C7Z270-CG

REV:1.00

BIOS LICENSE

MAC CODE

BAR CODE

RESET BUTTON

POWER BUTTON

U.2 CONNECTOR 2

U.2 CONNECTOR 1

I-SATA5

I-SATA4

I-SATA3

SYS_FAN2

SYS_FAN1

CPU_FAN2

SYS_FAN3

I-SATA1

USB 10/11 (3.1)

USB6/7

LAN

DVI

PCIE M.2 CONNECTOR 1

USB2/3

USB4/5

USB 8/9 (3.1)

X

PWR

HDD

LED LED

NIC

1

OH/FF X

RST

PWR

ON

PCIE M.2 CONNECTOR 2

ON:BIOS RECOVERY

OFF:NORMAL

JBR1

TPM/PORT80

INTRUSION

CHASSIS

JL1:

KB/MOUSE

USB 0/1

USB 12/13 (3.0)

I-SATA0

DIMMB2

DIMMB1

DIMMA2

DIMMA1

HDMI/DP

CPU SLOT1 PCI-E 3.0 X4 (IN X16)

PCH SLOT2 PCI-E 3.0 X1

CPU SLOT3 PCI-E 3.0 X8 (IN X16)

PCH SLOT4 PCI-E 3.0 X1

PCH SLOT5 PCI-E 3.0 X1

CPU SLOT6 PCI-E 3.0 X16

5V STBY POWER

JSTBY1:

JWD1:

JSD1:

2-3:DISABLE

1-2:ENABLE

JPL1:LAN

2-3:NMI

1-2:RST

WATCH DOG

2-3:ME MANUFACTURING MODE

CPU_FAN1

1-2:NORMAL

JPME2:

SATA DOM PWR

JTPM1:

JLED1:

3 PIN POWER LED

AUDIO FP

JBT1

CMOS CLEAR

SPEAKER:1-4

JD1:

BUZZER:3-4

JI2C1/JI2C2

ON :ENABLE

OFF:DISABLE

HD AUDIO

JF1

COM1

2-3:DISABLE

1-2:ENABLE

JPAC1:AUDIO

I-SATA2

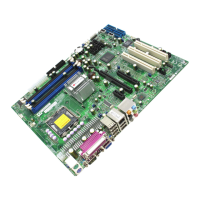

A. Backpanel USB 2.0 #0

B. Back panel USB 2.0 #1

C. Back panel USB 3.1 #8

D. Back panel USB 3.1 #9

E. Back panel USB 3.1 #10

F. Back panel USB 3.1 #11

G. USB 2.0 Header #2/3

H. USB 2.0 Header #4/5

I. USB 2.0 Header #6/7

J. USB 3.0 Header #12/13

Universal Serial Bus (USB)

Two Universal Serial Bus 2.0 ports (#0/1), three USB 3.1 ports (#8/9/10)

and one USB 3.1 'type C' port (#11) are located on the I/O back panel.

In addition, one USB 3.0 header (two ports: #12/13), and three USB 2.0

headers (six ports: #2/3, 4/5, 6/7) are also located on the motherboard

to provide front chassis access using USB cables (not included). See the

tables below for pin denitions.

Back Panel USB (2.0) #0/1, USB (3.1)

#8/9/10/11 Pin Denitions

Pin# Denition Pin# Denition

1 +5V 5 +5V

2 USB_PN1 6 USB_PN0

3 USB_PP1 7 USB_PP0

4 Ground 8 Ground

Front Panel USB (2.0) Header

#2/3/4/5/6/7 Pin Denitions

Pin # Denition Pin # Denition

1 +5V 2 +5V

3 USB_PN2 4 USB_PN3

5 USB_PP2 6 USB_PP3

7 Ground 8 Ground

9 Key 10 Ground

Front Panel USB (3.0) Header #12/13

Pin Denitions

Pin# Pin# Signal Name Description

1 19 VBUS Power

2 18 StdA_SSRX- SuperSpeed Receiver

3 17 StdA_SSRX+ Differential Pari

4 16 Ground Ground of PWR Return

5 15 StdA_SSTX- SuperSpeed Transmitter

6 14 StdA_SSTX+ Differential Pair

7 13 GND_DRAIN Ground for Signal Return

8 12 D- USB 2.0 Differential Pair

9 11 D+

G

H

I

J

A

B

C

D

E

F

Loading...

Loading...