13

Chapter 1: Introduction

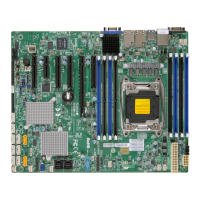

IPMI_LAN

USB0/1

LAN1

LAN2

USB6/7

(3.0)

JPL1

JSTBY1

JPG1

JTPM1

COM2

COM1

FAN4

JF1

JPH1

JPV1

JPW1

FAN1

JPI2C1

FAN2

FAN3

FANA

JPUSB1

USB10 (3.0)

USB8/9 (3.0)

USB4/5

I-SGPIO2

I-SGPIO1

JS1

JL1

USB2/3

JP3

JWD1

JPME2

JI2C2

JI2C1

JPB1

JBT1

BT1

JMD1

JNVI2C1

JIPMB1

LEDBMC

LEDPWR

LE8

LE1

JUIDB1

VGA

JPCIE4

JPCIE5

JPCIE6

CPU1 SLOT6 PCI-E 3.0 X16

CPU1 SLOT5 PCI-E 3.0 X8

CPU1 SLOT4 PCI-E 3.0 X8

FAN5

I-SATA3

SP1

I-SATA2

I-SATA1

I-SATA0

I-SATA5

I-SATA4

JSD2

JSD1

JPH2

DIMMA1

DIMMB1

DIMMD1

DIMMC1

CLOSE 1st

OPEN 1st

MAC CODE

BAR CODE BAR CODE

CPU

INTEL PCH

LAN

CONTROLLER

X10SRM-F/-TF

REV:1.01

Designed in the USA

SRW5

SRW4

SRW3

JVRM2

JVRM1

JOH1

JD1

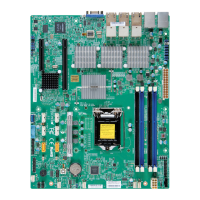

IPMI_LAN

USB0/1

USB10 (3.0)

LAN1

USB6/7 (3.0)

LAN2

JCOM1

JVGA

JUIDB1

LE1

JIPMB1

JPL1

JTPM1

FAN4

COM2

JSTBY1

JPV1

JPW1

JPI2C1

FAN2

FAN1

JVRM2

JPH2

FAN3

I-SATA5

USB8/9 (3.0)

SP1

DIMMC1

DIMMA1

DIMMD1

DIMMB1

JF1

JPB1

JNVI2C1

FANA

JI2C1

BT1

JI2C2

JBT1

JWD1

JPME2

USB2/3

JP3

JD1

JS1

I-SATA4

I-SATA3

JL1

USB4/5

JSD1

I-SGPIO1

I-SGPIO2

JPUSB1

LEDPWR

JPG1

JPH1

JVRM1

LE8

JMD1

JSD2

I-SATA2

I-SATA1

I-SATA0

LEDBMC

SRW5

SRW4

SRW3

FAN5

Quick Reference

Notes:

• See Chapter 2 for detailed information on jumpers, I/O ports, and JF1 front panel con-

nections.

• " " indicates the location of Pin 1.

• Jumpers/LED indicators not indicated are used for testing only.

• Please refer to the table on page 10 to see model variations.

• Use only the correct type of onboard CMOS battery as specied by the manufacturer. Do

not install the onboard battery upside down to avoid possible explosion.

JOH1

Loading...

Loading...