TB9100 Reciter Service Manual Network Circuitry 43

© Tait Electronics Limited January 2006

The bus monitor timer monitors the duration of bus cycles to ensure that

they are terminated within a reasonable time. If the timer expires, it asserts

the TEA

signal (see “MPC Bus Cycles” on page 48) to terminate the bus

cycle with an error condition. The bus monitor time-out period is

programmable up to 2040 bus clocks ie. approximately 32.6us at a 62.5MHz

bus clock.

The software watchdog timer provides a means of terminating a runaway

program. If the watchdog is not serviced by periodically by writing specific

data patterns to its service register, it eventually times out and issues a reset

or a non-maskable interrupt (NMI). The watchdog timer has a

programmable16-bit down counter, which is clocked from a divide-by-

2048 prescaler from the main system clock. Therefore, with a 125MHz

system clock, the watchdog time-out periods can range from approximately

16us through to approximately 1s.

The periodic interrupt timer (PIT), decrementer and time base are 16, 32

and 64-bit counters respectively. They can be used to generate interrupts at

specific times and are mainly used for operating system timing functions.

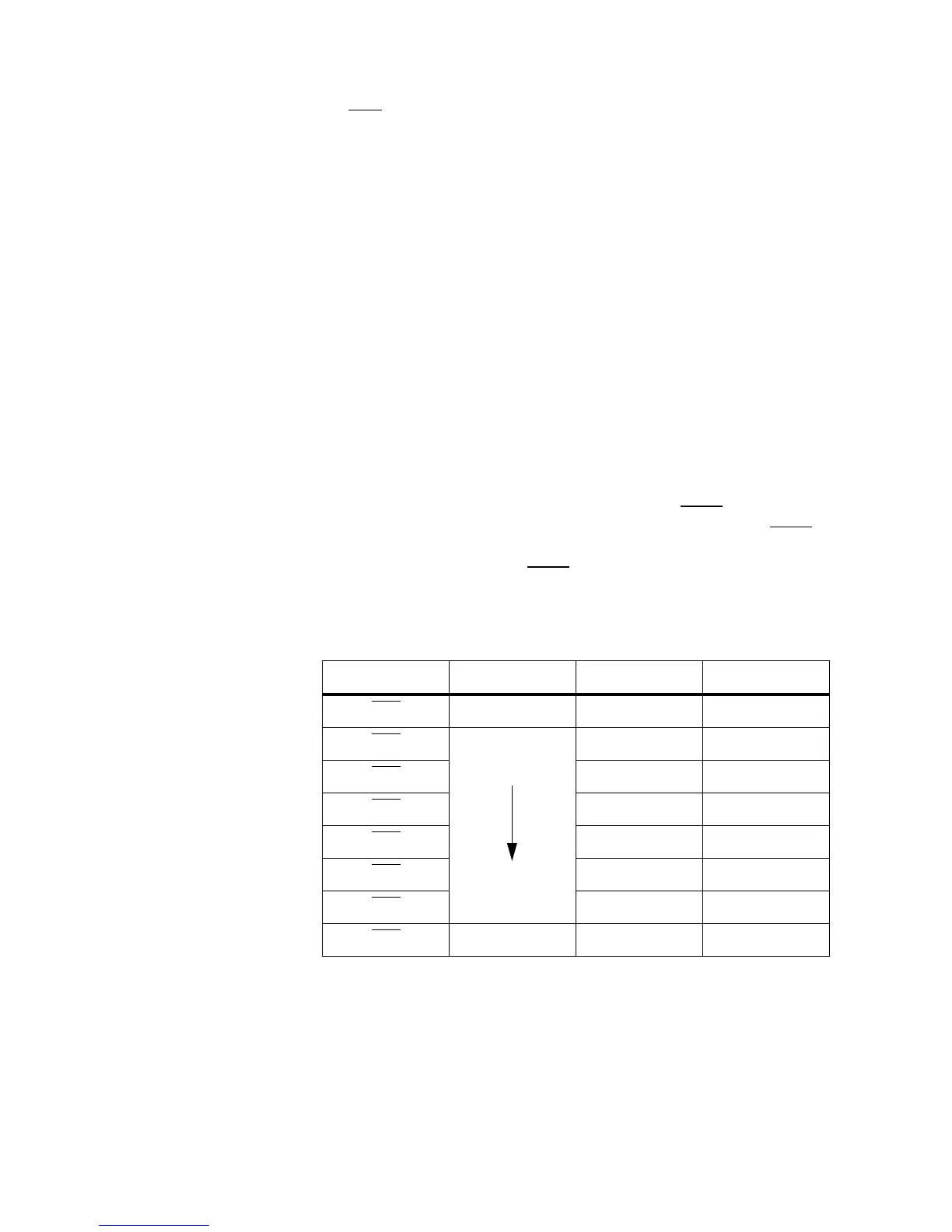

Interrupts Four of the eight levels of external interrupt inputs available on the MPC

are used in the ASIF, as detailed in Tabl e 5.1. All but IRQ0

can be masked

under software control to ignore that interrupt source. The pin for IRQ7

is

utilized as a clock input for the MII (see “Media Independent Interface

(MII)” on page 76); therefore IRQ7

must be masked to avoid numerous

spurious interrupts.

All interrupt inputs are active low and can be configured to be either edge

or level sensitive. The priority of the external interrupts is fixed, ie. a higher

priority interrupt request service routine cannot be interrupted by a lower

priority interrupt request. Interrupts from internal sources are combined

and prioritized along with external interrupts (see “Interrupt Controller”

on page 55).

Table 5.1 MPC Interrupt Sources

Interrupt Input Priority Type Source

IRQ0 Highest Non-maskable not used

IRQ1

Maskable 1 PPS

IRQ2

Maskable not used

IRQ3

Maskable DSP host port

IRQ4

Maskable Ethernet PHY

IRQ5

Maskable not used

IRQ6

Maskable E-lead

IRQ7

Lowest Maskable not used

Loading...

Loading...