44 Network Circuitry TB9100 Reciter Service Manual

© Tait Electronics Limited January 2006

Aside from the external interrupts, the interrupt controller also combines

and prioritizes interrupts from internal sources including the:

■ software watchdog timer

■ PCMCIA interface

■ communications processor (see “Interrupt Controller” on page 55)

PCMCIA Interface The MPC incorporates logic to control the interface to two PCMCIA card

sockets. This is not used in the ASIF but the pins (IP_A[0..7]), normally

used for sensing the PCMCIA card status, are used for sensing the general-

purpose digital inputs (see “Parallel Ports” on page 59 and “General-

purpose Digital Inputs” on page 72). These pins feature change-of-state

sensing, generating an interrupt on a change of pin state. This allows the

software to respond quickly to changes without the high overhead of

continuous polling.

5.2.3 RISC Reset and Configuration

MPC Reset The MPC supports several levels of resets that can be initiated internally to

the MPC or driven by external devices. The different levels of resets are

primarily used to enable software debugging without disturbing the internal

state of some parts of the MPC. In particular, a soft reset retains the major

MPC system configuration and maintains the memory controller refresh

operation (see “SDRAM Refresh Cycles” on page 64), so that the dynamic

memory contents are not lost.

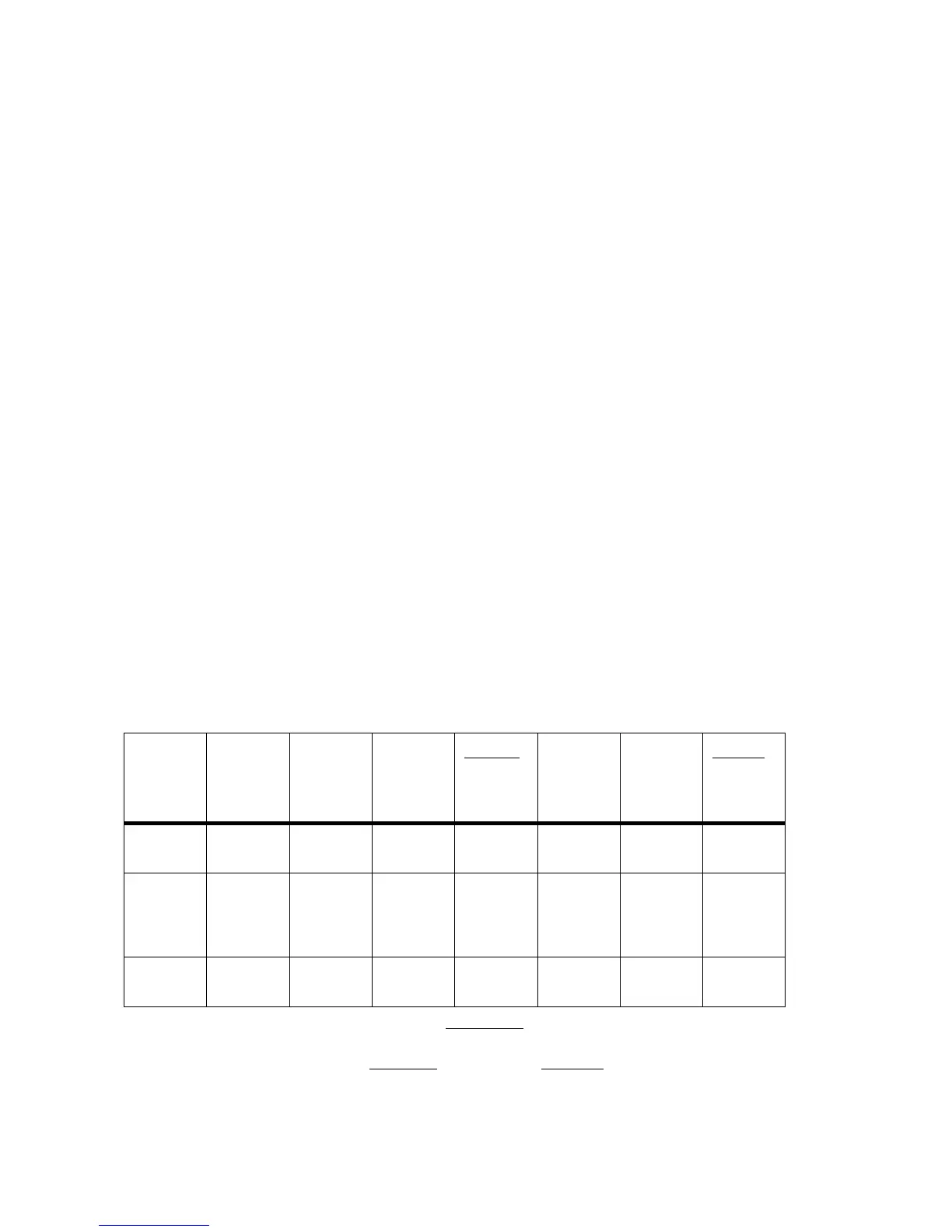

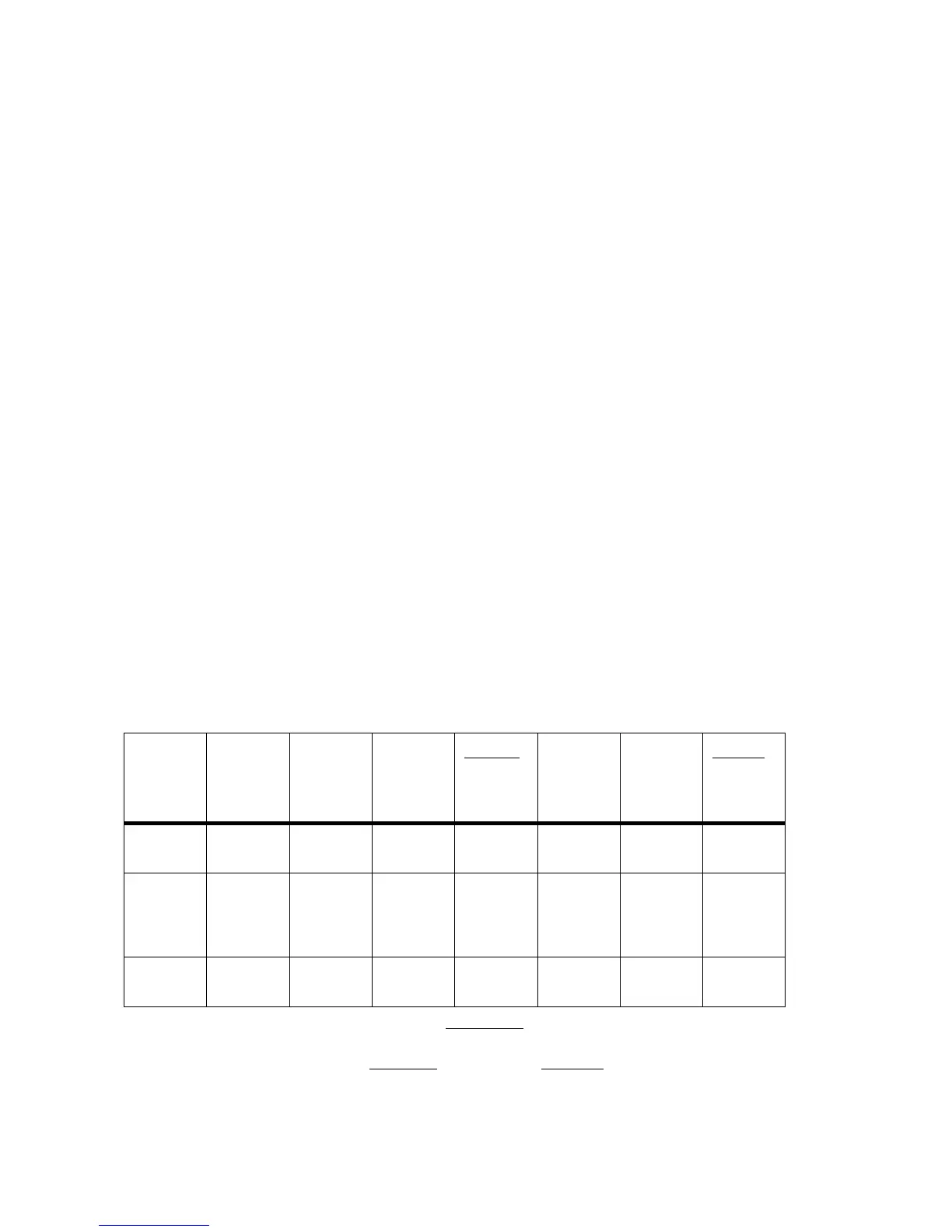

The sources of reset used in the ASIF and their effects are detailed in

Tabl e 5 .2.

On power up the MPC’s PORESET

input is taken low by the power supply

circuitry (see “Power-on Reset” on page 85). In response, the MPC drives

its hard reset (HRESET

) and soft reset (SRESET) outputs low, resetting any

external circuitry connected to them.

Table 5.2 Reset Responses

Reset

source

PLL reset

System

config

reset

Clock

module

reset

HRESET

driven

Debug

port

config

Other

internal

logic

reset

SRESET

driven

Power-on

reset

YYYYYYY

Software

watchdog,

debug port

hard reset

NYYYYYY

Debug port

soft reset

NNNNYYY

Loading...

Loading...