48 Network Circuitry TB9100 Reciter Service Manual

© Tait Electronics Limited January 2006

MPC Bus Cycles

The MPC is capable of arbitrating with other external bus servers for control

of the address and data buses using the Bus Request (BR

), Bus Grant (BG)

and Bus Busy (BB

) pins. External bus servers are not used in the ASIF

design, so the MPC is configured (see “MPC Configuration” on page 45)

for internal arbitration, and the bus arbitration pins are pulled up to their

inactive high state.

Assuming that the MPC has obtained ownership of the bus, it starts a bus

cycle by outputting the address and the transfer attributes detailed in

Tabl e 5 .6. The transfer start signal (TS

) is asserted to indicate the start of a

bus cycle.

Except for the RD/WR

line, none of the above transfer attributes are used

in the ASIF external memory logic, but they may be used internally by the

memory controllers (see “Memory Controllers” on page 49) to determine

the cycle type. Some are available on test points to facilitate hardware and

program debugging.

When the memory or peripheral devices has output/input the data to/from

the bus, it tells the MPC to terminate the bus cycle by asserting the transfer

acknowledge signal (TA

). For devices that do not have a suitable transfer

acknowledge signal, this can be provided internally by the relevant memory

controller (see “Memory Controllers” on page 49). The sequence of

operations for a single (ie. non-burst) bus write cycle is shown in Figure 5.4.

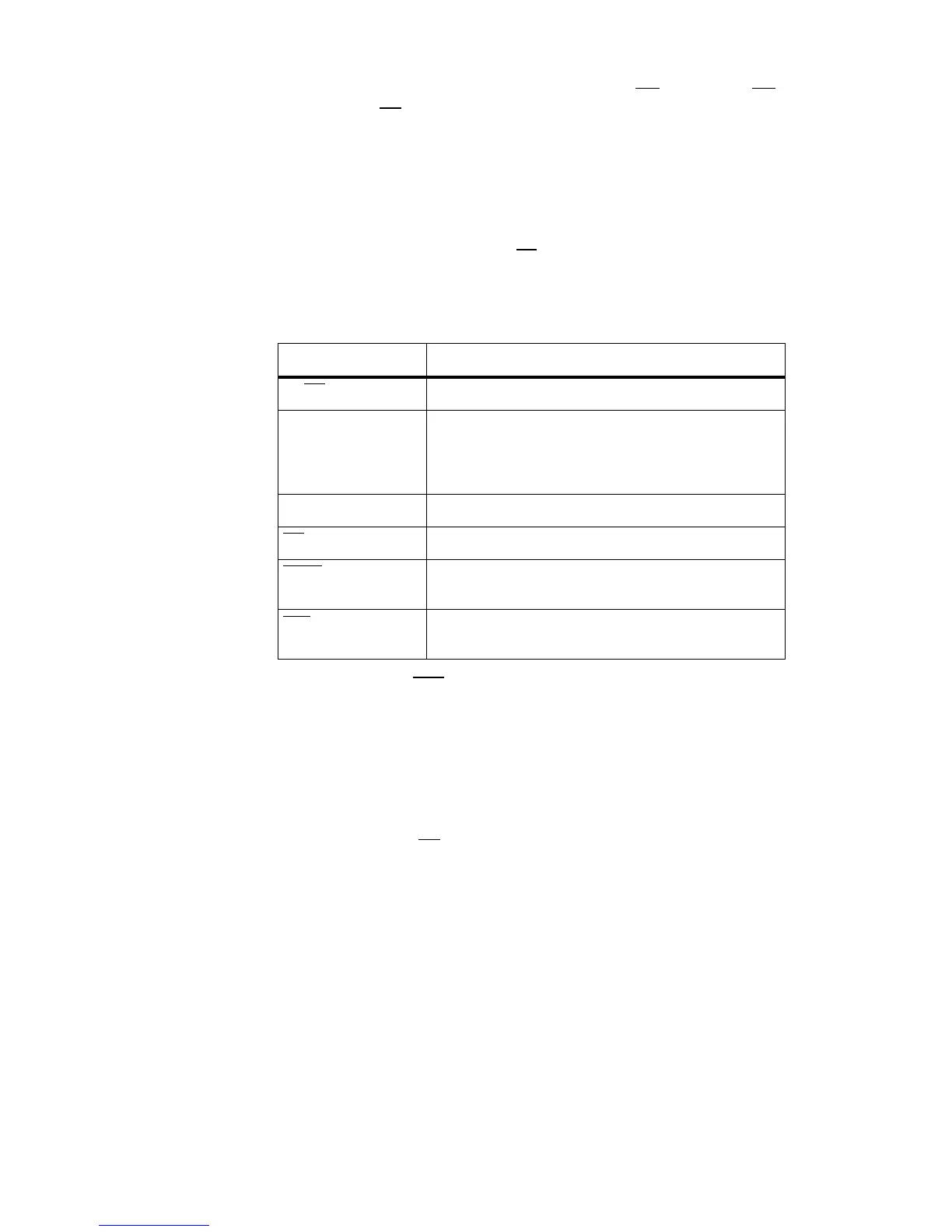

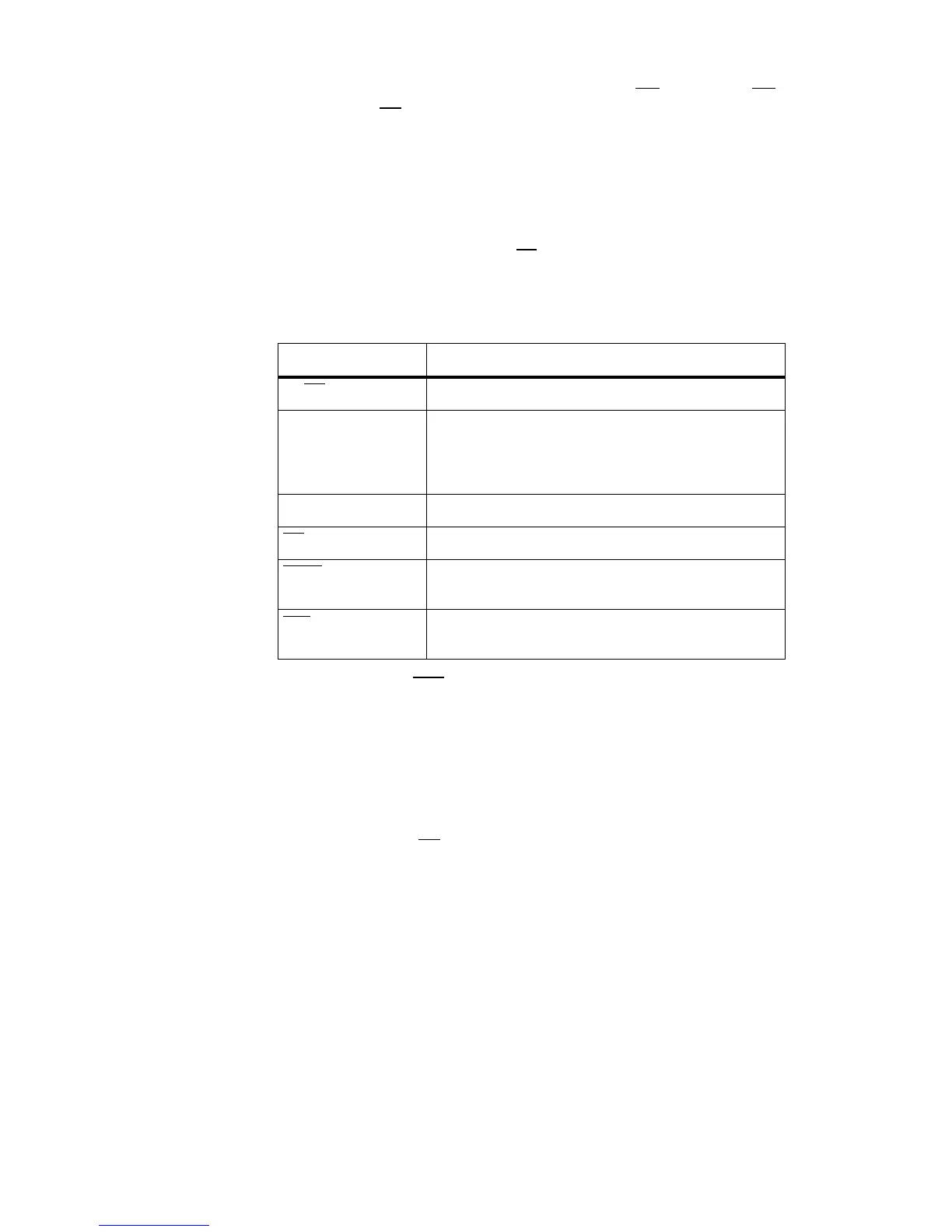

Table 5.6 Bus Cycle Transfer Attributes

Transfer Attribute Function

RD/WR Read/write cycle

AT[0..3] Address type modifier 0: Core/CPM access

Address type modifier 1: User/supervisor access

Address type modifier 2: Instruction/Data

Address type modifier 3: Reservation/Program Trace

TSIZ[0..1] Transfer size (see Ta ble 5. 5)

STS

Special transfer start: used for debugging purposes

BURST

Burst transfer: indicates memory cycle is a burst operation

(see “SDRAM Burst Cycles” on page 64)

BDIP

Burst data in progress: indicates another data transfer is

expected

Loading...

Loading...