66 Network Circuitry TB9100 Reciter Service Manual

© Tait Electronics Limited January 2006

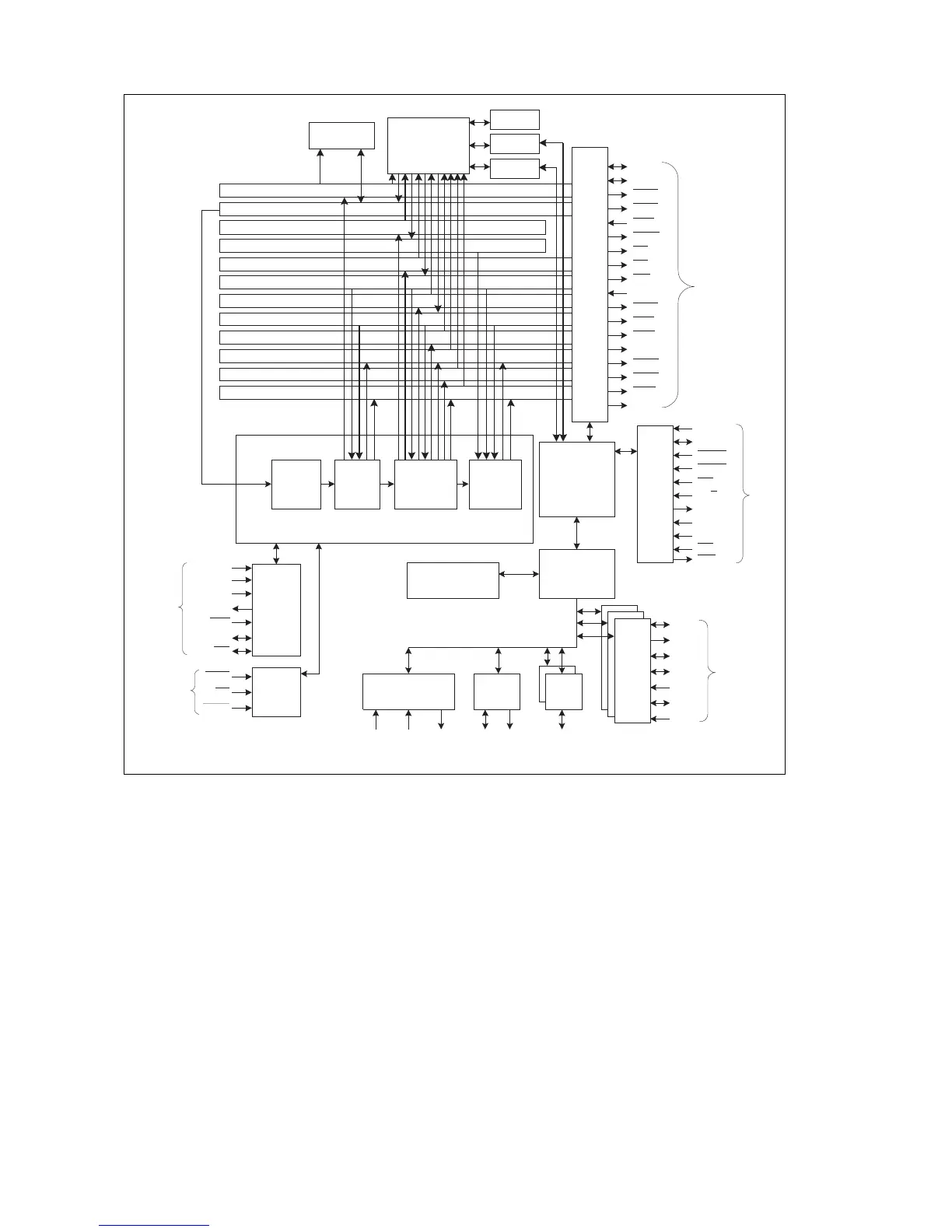

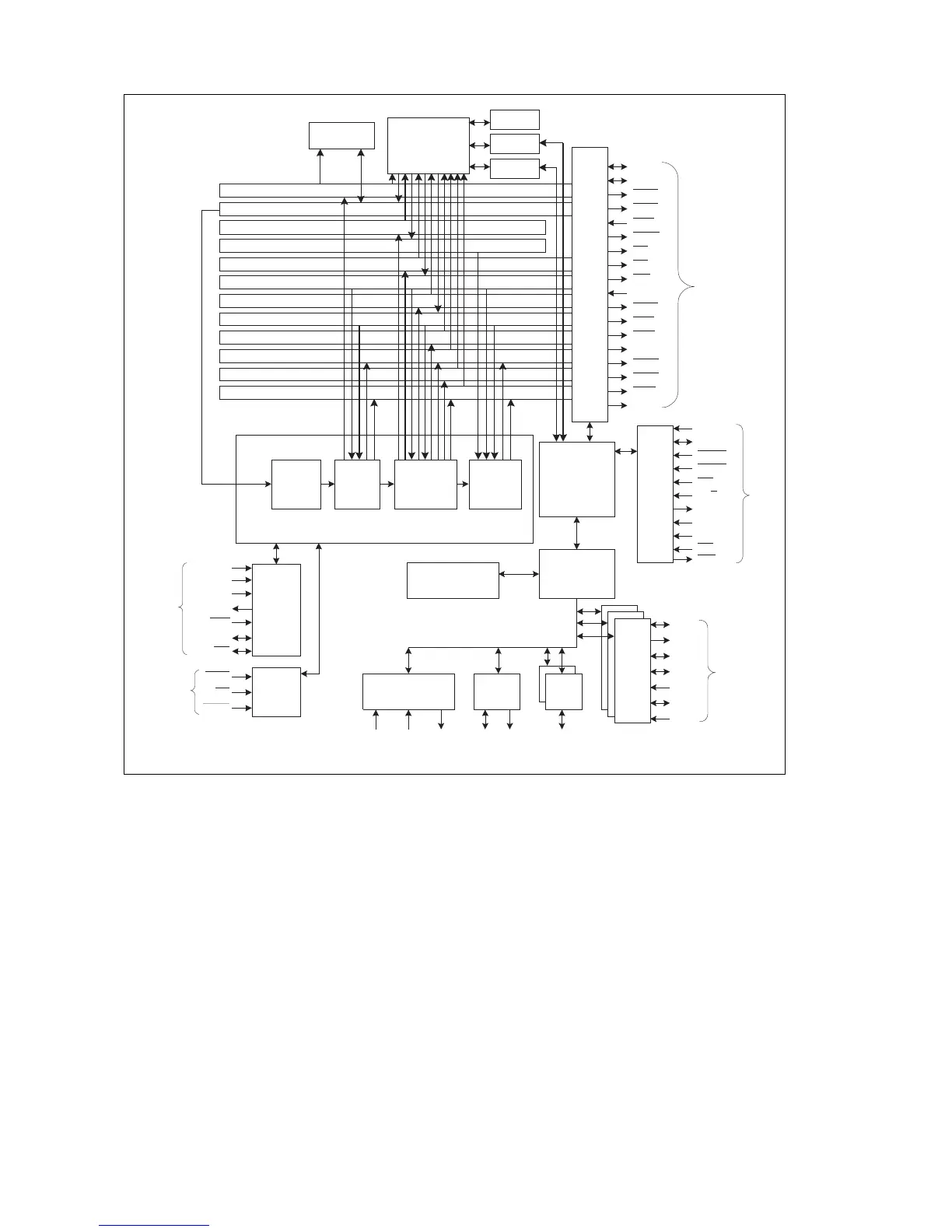

Processor Core

The TMS320VC5510 DSP has a 16-bit core with extensive instruction

pipelining for high performance. See the CPU architecture description

(reference 9) for details. Internally, the DSP utilizes a Harvard architecture

with separate sets of address and data buses for program code and data

accesses. The program address bus is 24 bits wide while the program data bus

is 32 bits wide. Multiple internal data buses, each 16 bits wide, and address

buses, each 24 bits wide, enable simultaneous data fetches or writes to

multiple memory blocks (see “Internal Memory” on page 68).

Where a program code fetch or data access cannot be satisfied from the

internal memory space, it is routed to external memory through the external

memory interface (EMIF) controller. For external accesses, both program

and data accesses occur over a unified 32 bit data bus and 22 bit address bus,

ie. a von Neumann type architecture.

Figure 5.7 DSP Block Diagram

EHPI

DMA

Controller

CPU

Instruction

Buffer

Unit (IU)

Program

Flow Unit

(PU)

Address

Data Flow

Unit (AU)

Data

Computation

Unit (DU)

Program Address Bus PAB (24)

Program Data Bus PB (32)

Data Read Address Bus B [BAB] (24)

Data Read Bus B [BB] (16)

Data Read Address Bus C [CAB] (24)

Data Read Bus C [CB] (16)

Data Read Address Bus D [DAB] (24)

Data Read Bus D [DB] (16)

Data Write Address Bus E [EAB] (24)

Data Write Bus E [EB] (16)

Data Write Address Bus F [FAB] (24)

Data Write Bus F [FB] (16)

Instruction

Cache

Internal

Memory

Interface

ROM

16 K Words

SARAM

32 K Words

DARAM

128 K Words

EXTERNAL

MEMORY

INTERFACE

HOST

PORT

Peripheral

Controller

Power

Management

McBSP

Clock

Generation

GPIO Timer

CLKMD CLKIN CLKOUT IO[7:0] XF TIN/TOUT

Interrupt

Control

Emulation

Control

McBSP

PORTS

FSX

DX

CLKX

FSR

DR

CLKR

CLKS

RESET

NMI

INT[5:0]

INTERRUPTS

JTAG

HA[19:0]

HD[15:0]

HBE[1:0]

HDS[2:1]

HCS

HR/W

HRDY

HMODE

HCNTL[1:0]

HAS

HINT

A[21:0]

D[31:0]

CE[3:0]

BE[3:0]

HOLD

HOLDA

ARE

AOE

AWE

ARDY

SSADS

SSOE

SSWE

CLKMEM

SDRAS

SDCAS

SDWE

SDA10

TCK

TMS

TDI

TDO

TRST

EMU0

EMU1/OFF

Loading...

Loading...