Theory of Operation—2465B/2467B Service

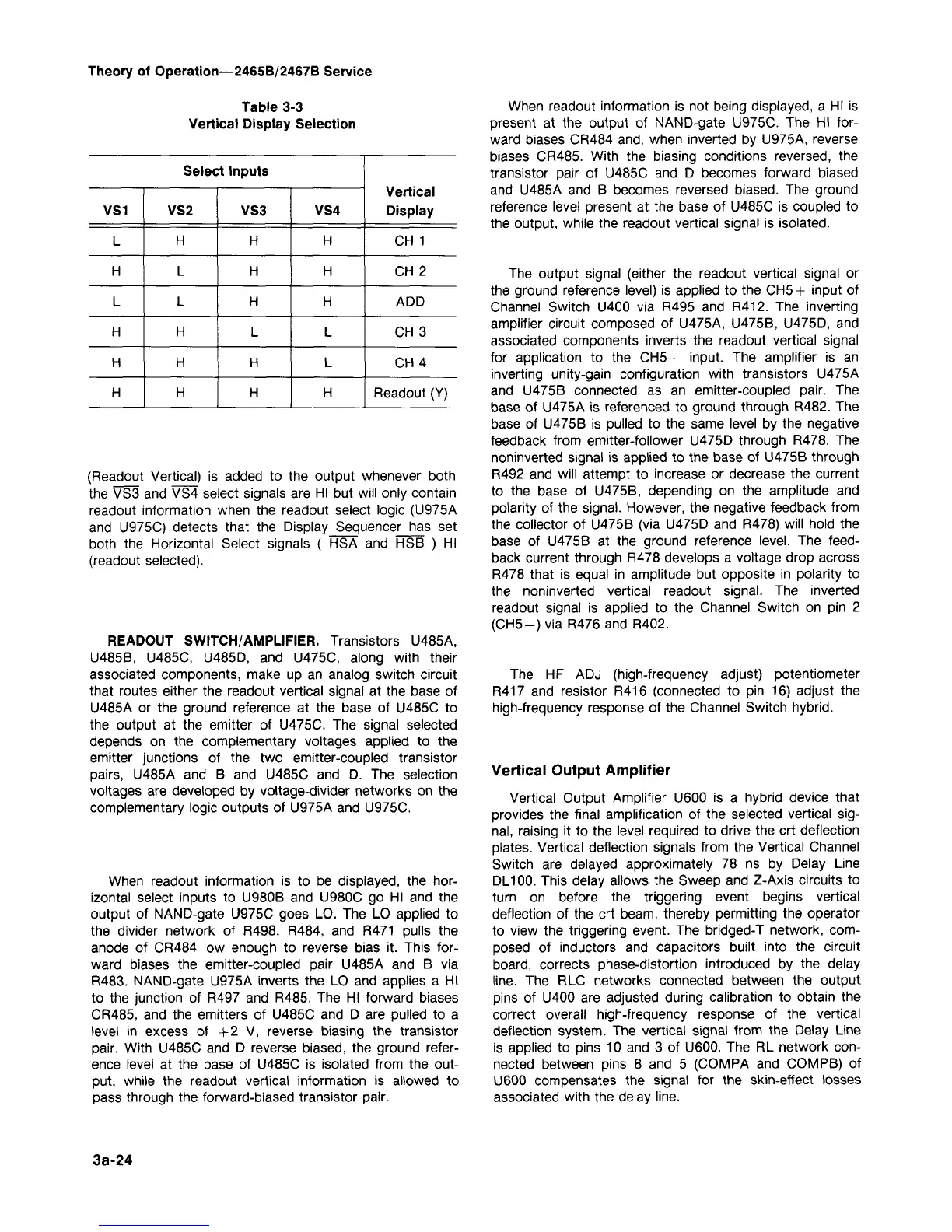

Table 3-3

Vertical Display Selection

Select Inputs

VS1

L

H

L

H

H

H

VS2

H

L

L

H

H

H

VS3

H

H

H

L

H

H

VS4

H

H

H

L

L

H

Vertical

Display

CH 1

CH 2

ADD

CH 3

CH4

Readout (Y)

(Readout Vertical) is added to the output whenever both

the VS3 and VS4 select signals are HI but will only contain

readout information when the readout select logic (U975A

and U975C) detects that the Display Sequencer has set

both the Horizontal Select signals ( HSA and HSB ) HI

(readout selected).

READOUT SWITCH/AMPLIFIER. Transistors U485A,

U485B,

U485C, U485D, and U475C, along with their

associated components, make up an analog switch circuit

that routes either the readout vertical signal at the base of

U485A or the ground reference at the base of U485C to

the output at the emitter of U475C. The signal selected

depends on the complementary voltages applied to the

emitter junctions of the two emitter-coupled transistor

pairs,

U485A and B and U485C and D. The selection

voltages are developed by voltage-divider networks on the

complementary logic outputs of U975A and U975C.

When readout information is to be displayed, the hor-

izontal select inputs to U980B and U980C go HI and the

output of NAND-gate U975C goes LO. The LO applied to

the divider network of R498, R484, and R471 pulls the

anode of CR484 low enough to reverse bias it. This for-

ward biases the emitter-coupled pair U485A and B via

R483.

NAND-gate U975A inverts the LO and applies a HI

to the junction of R497 and R485. The HI forward biases

CR485, and the emitters of U485C and D are pulled to a

level in excess of +2 V, reverse biasing the transistor

pair. With U485C and D reverse biased, the ground refer-

ence level at the base of U485C is isolated from the out-

put, while the readout vertical information is allowed to

pass through the forward-biased transistor pair.

When readout information is not being displayed, a HI is

present at the output of NAND-gate U975C. The HI for-

ward biases CR484 and, when inverted by U975A, reverse

biases CR485. With the biasing conditions reversed, the

transistor pair of U485C and D becomes forward biased

and U485A and B becomes reversed biased. The ground

reference level present at the base of U485C is coupled to

the output, while the readout vertical signal is isolated.

The output signal (either the readout vertical signal or

the ground reference level) is applied to the CH5+ input of

Channel Switch U400 via R495 and R412. The inverting

amplifier circuit composed of U475A, U475B, U475D, and

associated components inverts the readout vertical signal

for application to the CH5— input. The amplifier is an

inverting unity-gain configuration with transistors U475A

and U475B connected as an emitter-coupled pair. The

base of U475A is referenced to ground through R482. The

base of U475B is pulled to the same level by the negative

feedback from emitter-follower U475D through R478. The

noninverted signal is applied to the base of U475B through

R492 and will attempt to increase or decrease the current

to the base of U475B, depending on the amplitude and

polarity of the signal. However, the negative feedback from

the collector of U475B (via U475D and R478) will hold the

base of U475B at the ground reference level. The

feed-

back current through R478 develops a voltage drop across

R478 that is equal in amplitude but opposite in polarity to

the noninverted vertical readout signal. The inverted

readout signal is applied to the Channel Switch on pin 2

(CH5-)via R476and R402.

The HF ADJ (high-frequency adjust) potentiometer

R417 and resistor R416 (connected to pin 16) adjust the

high-frequency response of the Channel Switch hybrid.

Vertical Output Amplifier

Vertical Output Amplifier U600 is a hybrid device that

provides the final amplification of the selected vertical

sig-

nal,

raising it to the level required to drive the crt deflection

plates. Vertical deflection signals from the Vertical Channel

Switch are delayed approximately 78 ns by Delay Line

DL100.

This delay allows the Sweep and Z-Axis circuits to

turn on before the triggering event begins vertical

deflection of the crt beam, thereby permitting the operator

to view the triggering event. The bridged-T network, com-

posed of inductors and capacitors built into the circuit

board,

corrects phase-distortion introduced by the delay

line.

The RLC networks connected between the output

pins of U400 are adjusted during calibration to obtain the

correct overall high-frequency response of the vertical

deflection system. The vertical signal from the Delay Line

is applied to pins 10 and 3 of U600. The RL network

con-

nected between pins 8 and 5 (COMPA and COMPB) of

U600 compensates the signal for the skin-effect losses

associated with the delay line.

3a-24

Loading...

Loading...