LE910Cx Hardware Design Guide

1VV0301298 Rev.40 Page 82 of 149 2023-03-16

Not Subject to NDA

Sample rates of 8 kHz and 16 kHz

I2S

Master mode

Sample rate 8KHz, 16KHz

Sample-width is 16bit only.

Supported I2S standard only - Phillips I2S Bus Specifications revised June 5, 1996

In addition to the DVI port, the LE910Cx module provides a master clock signal (REF_CLK

on Pin B12) which can either provide a reference clock to an external codec or form an

PCM/I2S interface together with the DVI port where the REF_CLK acts as the MCLK.

The REF_CLK default frequency is 12.288 MHz.

When using the DVI with REF_CLK as PCM/I2S interface, 12.288 MHz is 256 x fs (where fs

= 48 kHz)

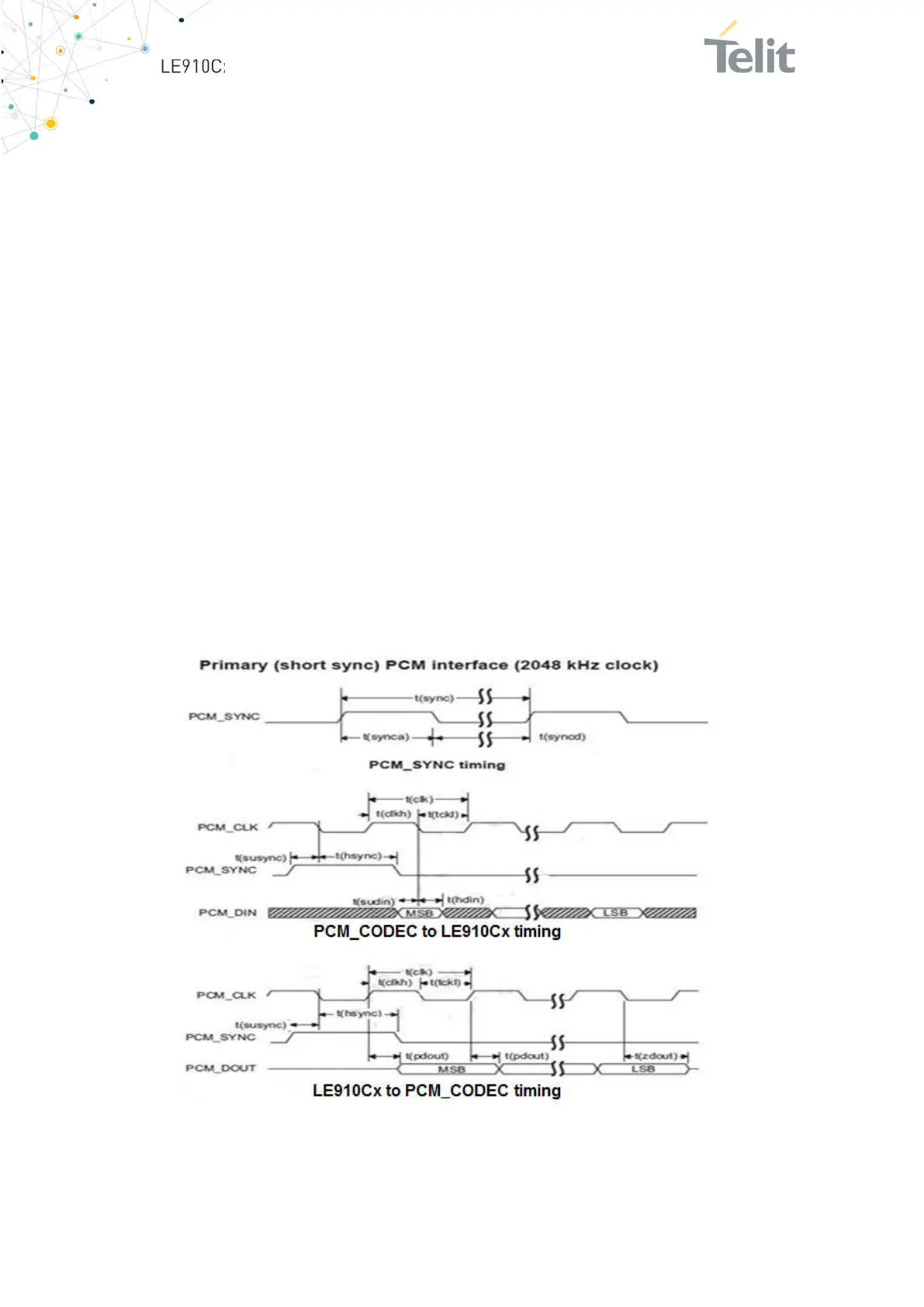

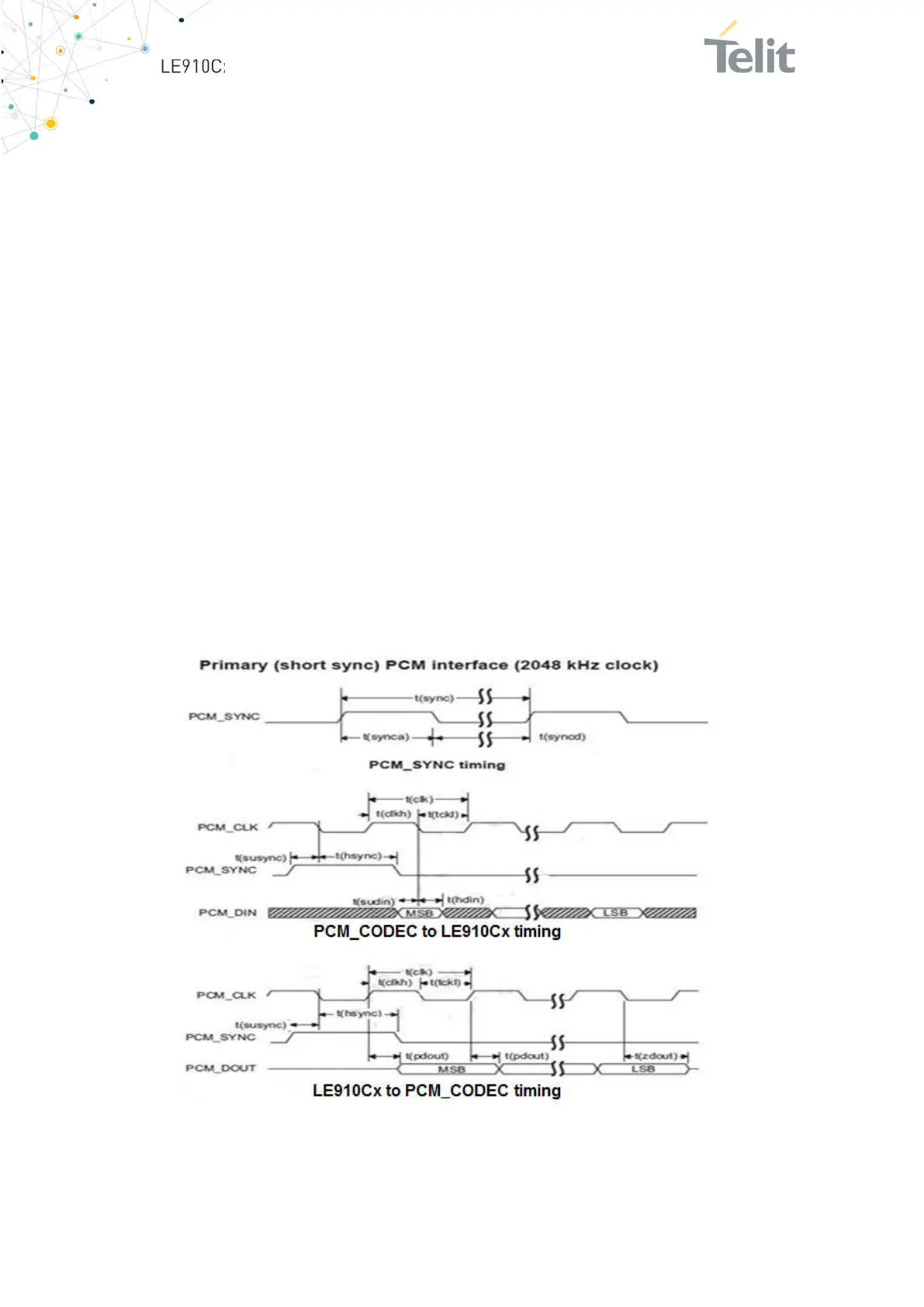

8.6.1.1. Short Frame Timing Diagrams

Figure 20: Primary PCM Timing

Loading...

Loading...