LE910Cx Hardware Design Guide

1VV0301298 Rev.40 Page 83 of 149 2023-03-16

Not Subject to NDA

Parameter Comments

Min Typ Max Unit

t(sync) PCM_SYNC cycle time - 125 - µs

t(synca) PCM_SYNC asserted time - 488 - ns

t(syncd) PCM_SYNC de-asserted time - 124.5 - µs

t(clk) PCM_CLK cycle time - 488 - ns

t(clkh) PCM_CLK high time - 244 - ns

t(clkl) PCM_CLK low time - 244 - ns

t(sync_offset)

PCM_SYNC offset time to

PCM_CLK falling

- 122 - ns

t(sudin)

PCM_DIN setup time to

PCM_CLK falling

60 - - ns

t(hdin)

PCM_DIN hold time after

PCM_CLK falling

60 - - ns

t(pdout)

Delay from PCM_CLK rising to

PCM_DOUT valid

- - 60 ns

t(zdout)

Delay from PCM_CLK falling to

PCM_DOUT HIGH-Z

- - 60 ns

Table 34: PCM_CODEC Timing Parameters

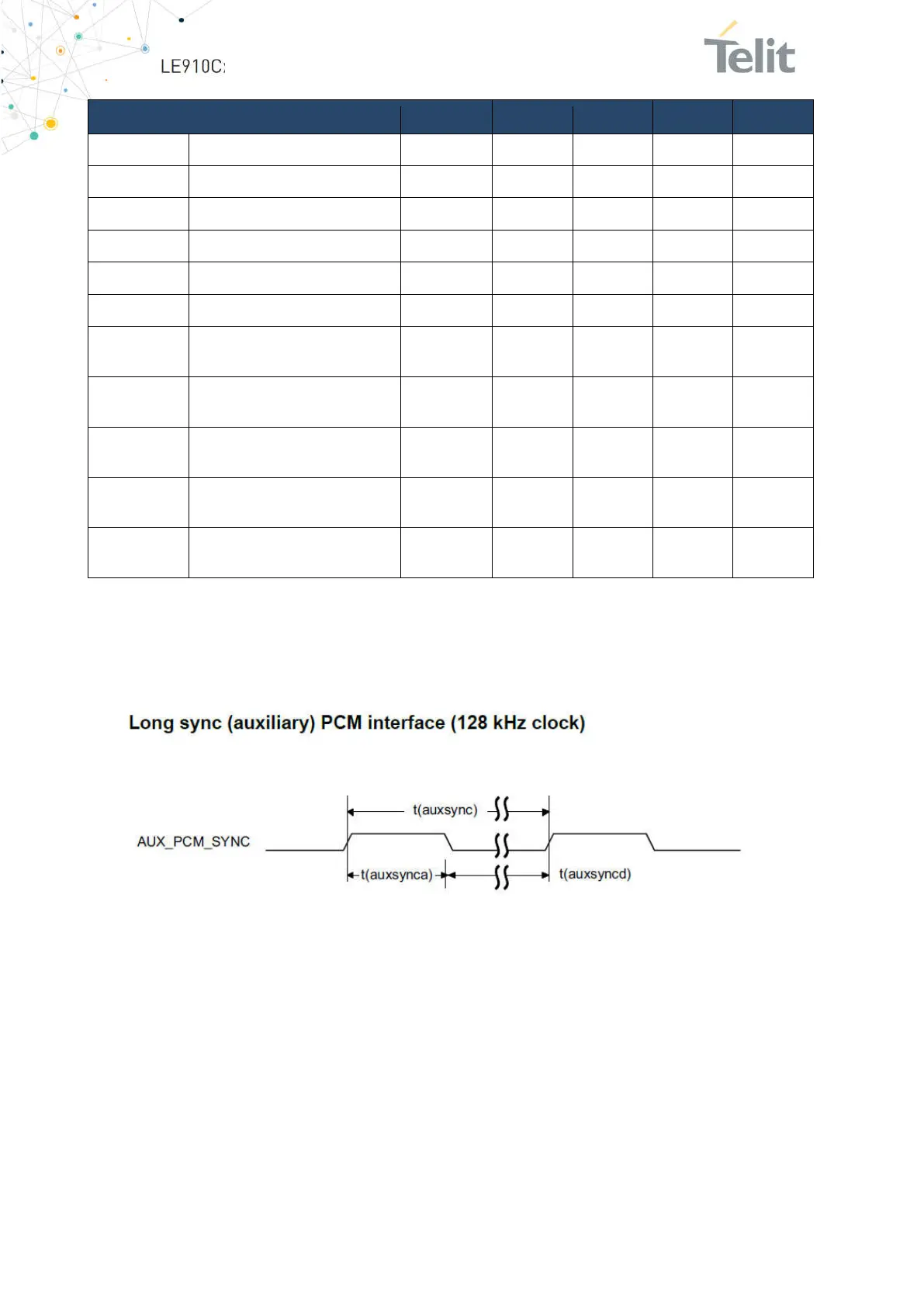

8.6.1.2. Long Frame Timing Diagrams

Loading...

Loading...