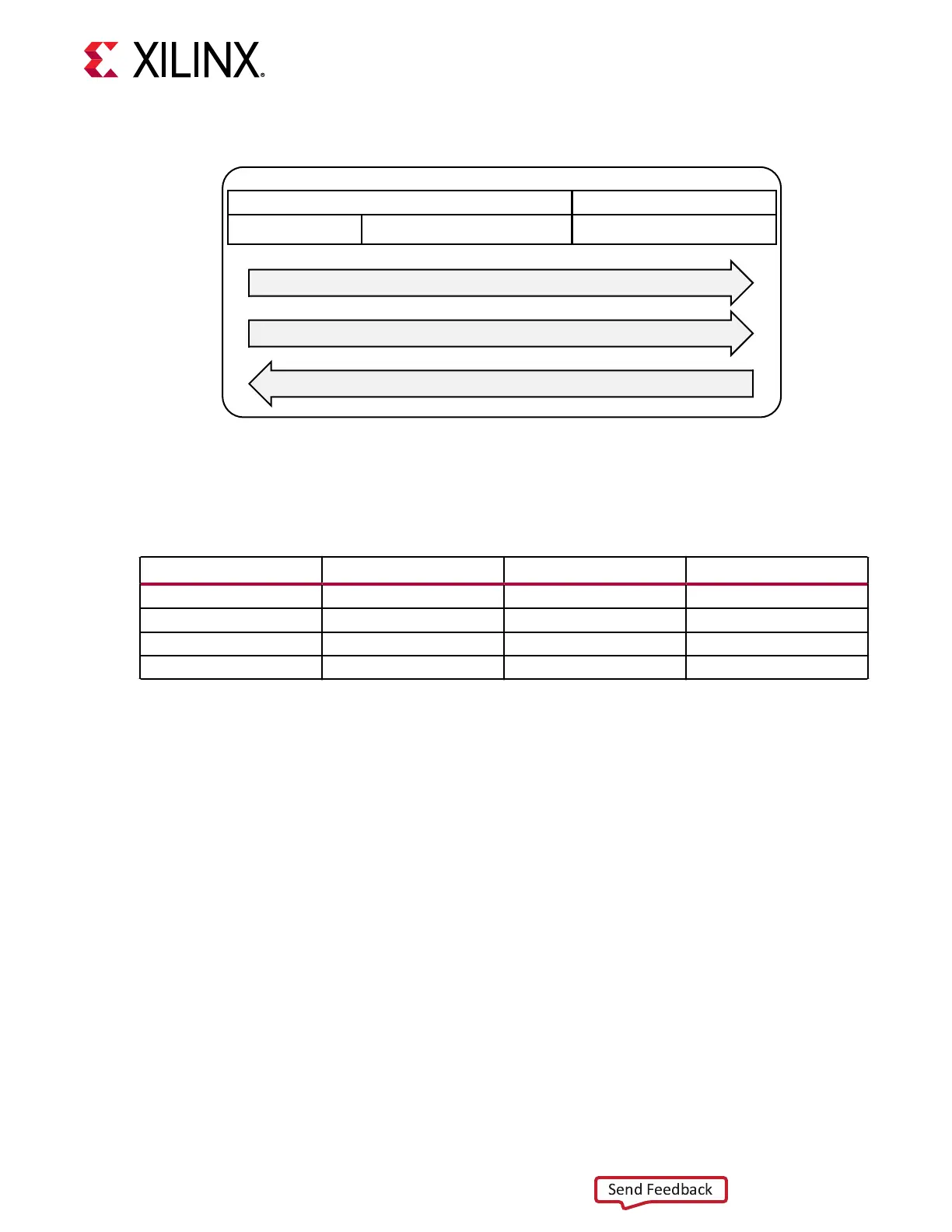

Figure 3: Alveo Data Center Accelerator Card Design Flows

High complexity

Slowest

High

Simplicity

Time to Market

Hardware Expertise Required

Complexity abstracted

Fastest

Low

RTL Flow HLx Flow (IP integrator)

Traditional Flows

Target Platform

Vitis

X22272-020419

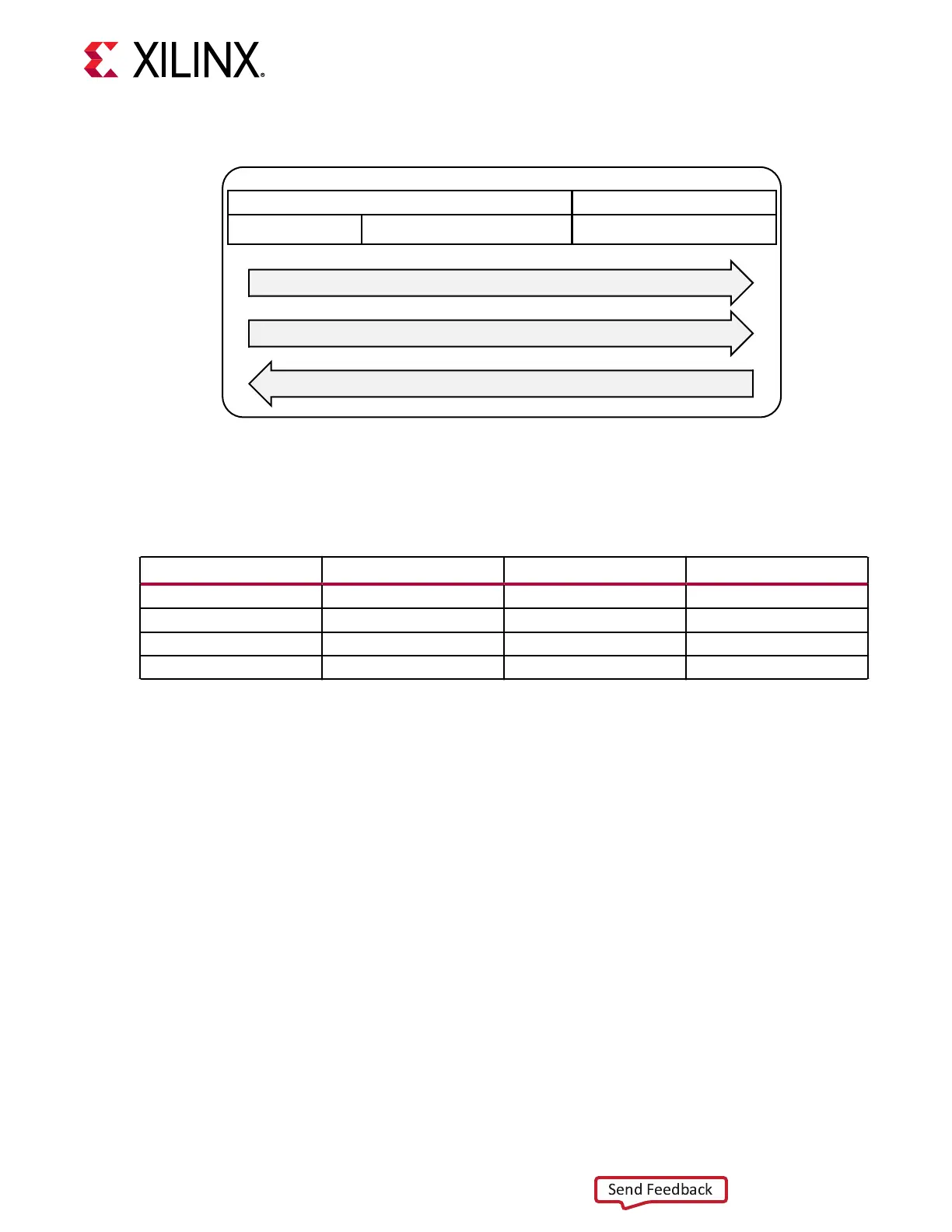

Requirements for the dierent design ows are listed in the following table.

Table 1: Requirements to Get Started with Alveo Data Center Accelerator Card Design

Flows

RTL Flow HLx Flow Vitis

Flow documentation UG949

1

UG895

2

UG1301

3

Hardware documentation UG1289 UG1289 N/A

Vivado tools support Board support XDC Board support XDC N/A

Programming the FPGA Vivado Hardware Manager Vivado Hardware Manager

Notes:

1. UltraFast Design Methodology Guide for the Vivado Design Suite (UG949).

2. Vivado Design Suite User Guide: System-Level Design Entry (UG895). See “Using the Vivado Design Suite Platform Board

Flow” in Chapter 2 and Appendix A.

3. Getting Started with Alveo Data Center Accelerator Cards (UG1301).

For either the RTL or HLx ow, designers can start by targeng the Alveo Data Center

accelerator card in the Vivado

®

tools. In the Vivado Design Suite, select Create New Project →

RTL Project, and then select the Alveo Data Center accelerator U200 card as shown in the

following gure.

Chapter 1: Introduction

UG1289 (v1.1.1) November 20, 2019 www.xilinx.com

Alveo U200 and U250 Accelerator Cards 10

Loading...

Loading...