70 www.xilinx.com ML605 Hardware User Guide

UG534 (v1.9) February 26, 2019

Chapter 1: ML605 Evaluation Board

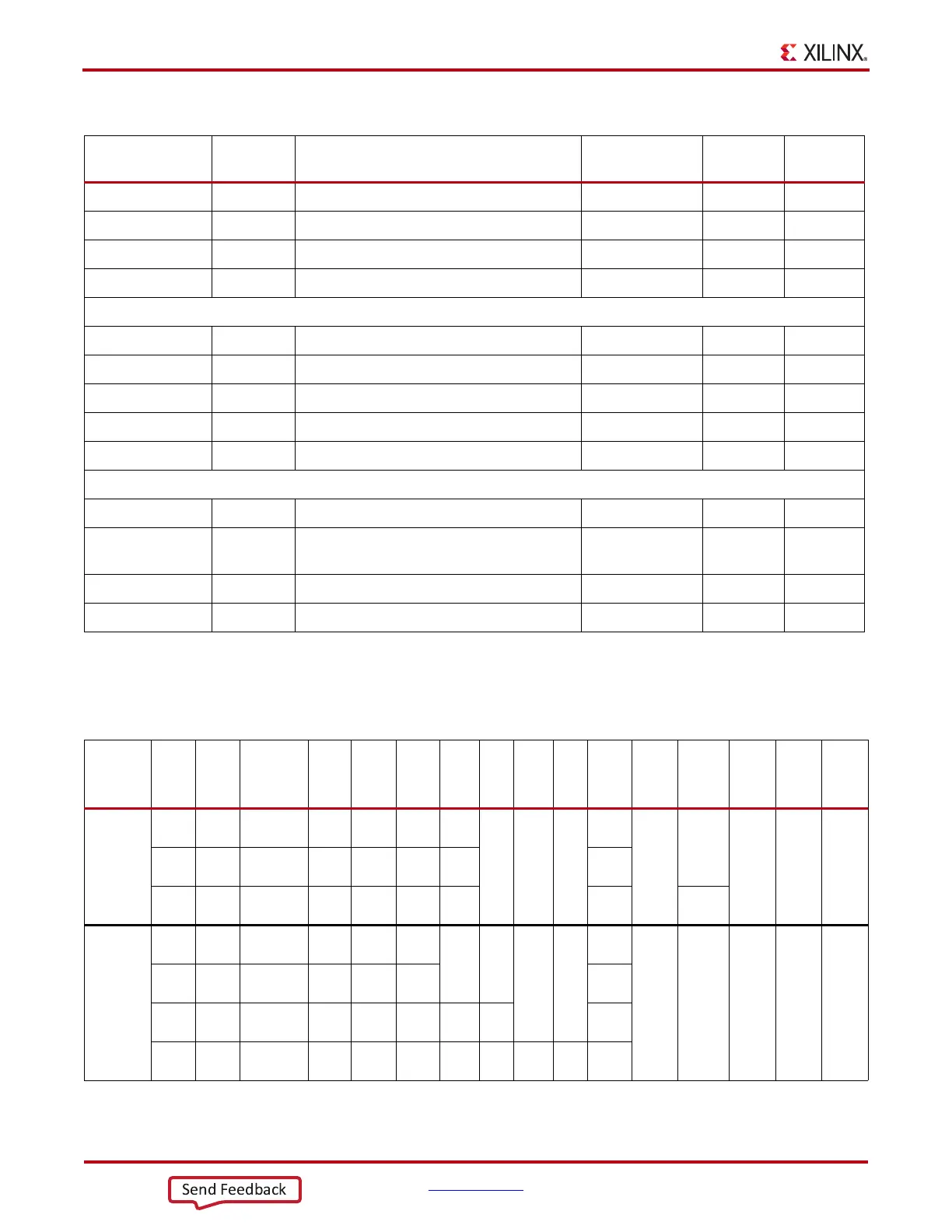

Table 1-31: Onboard Power System Devices

Device Type

Reference

Designator

Description

Power Rail

Net Name

Power Rail

Voltage

Schematic

Page

UCD9240PFC

(1)

U24 PMBus Controller - Core (Addr = 52) 35

PTD08A020W U42 20A 0.6V - 3.6V Adj. Switching Regulator VCCINT_FPGA 1.00V 36

PTD08A020W U43 20A 0.6V - 3.6V Adj. Switching Regulator VCC2V5_FPGA 2.50V 37

PTD08A010W U91 10A 0.6V - 3.6V Adj. Switching Regulator VCCAUX 2.50V 38

UCD9240PFC

(2)

U25 PMBus Controller - Aux (Addr = 53) 40

UCD7230RGWR U35 6A 0.6V - 3.6V Adj. Switching Regulator MGT_AVCC 1.00V 41

UCD7230RGWR U36 6A 0.6V - 3.6V Adj. Switching Regulator MGT_AVTT 1.20V 42

PTD08A010W U20 10A 0.6V - 3.6V Adj. Switching Regulator VCC_1V5 1.50V 43

PTD08A010W U21 10A 0.6V - 3.6V Adj. Switching Regulator VCC_3V3 3.30V 44

TPS79518DCQR U79 500 mA Fixed Linear Regulator VCC_1V8 1.80V 45

TPS51200DRCT U17 3A DDR3 VTERM Tracking Linear

Regulator

VTTDDR 0.75V 45

TPS51200DRCT U17 10 mA Tracking Reference output VTTVREF 0.75V 45

TL1963 U8 1.5A Fixed Linear Regulator VCC5 5.00V 35

Notes:

1. See Table 1-32., part 1 (addr 52)

2. See Table 1-32., part 2 (addr 53)

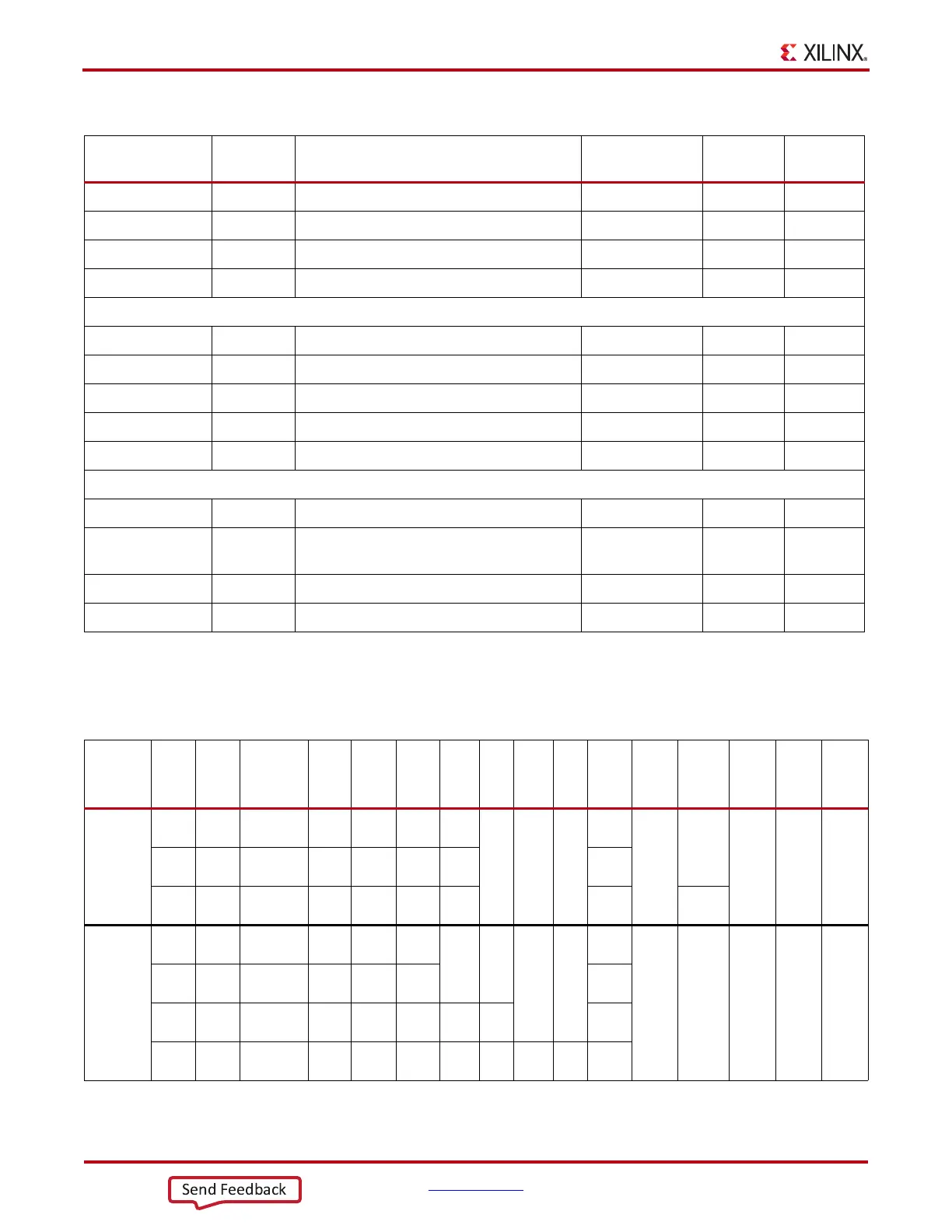

Table 1-32: Power Rail Specifications (UCD9240 PMBus Controllers at Addresses 52 and 53)

Device Rail #

Rail

Name

Schematic

Rail Name

Vout

(V)

PG On

(V)

PG Off

(V)

On

Delay

(ms)

Rise

(ms)

Off

Delay

(ms)

Fall

(ms)

Vout

Over

Fault

(V)

Response

Iout

Over

Fault

(A)

Response

Temp

Over

Fault

(°C)

Response

UCD9240

(Addr 52)

1

Rail

#1

VCCINT 1 0.925 0.9 5

10510

1.1

Shut

down

14

Shut

down

80

Shut

down

2

Rail

#2

VCC2V5 2.5 2.313 2.25 10 2.75

3

Rail

#3

VCCAUX 2.5 2.325 2.25 5 2.8 9

UCD9240

(Addr 53)

1

Rail

#1

MGT

_AVCC

1.025 0.948 0.923

520

510

1.128

Shut

down

14.5

Shut

down

80

Shut

down

2

Rail

#2

MGT

_AVTT

1.25 1.156 1.125 1.375

3

Rail

#3

VCC1V5

_FPGA

1.5 1.388 1.35 10 10 1.65

4

Rail

#4

VCC3V3 3.3 3.052 2.97 5 5 0 0 3.63

Loading...

Loading...