SP605 Hardware User Guide www.xilinx.com 37

UG526 (v1.1.1) February 1, 2010

Detailed Description

References

See the ST Micro M24C08 Data Sheet for more information. [Ref 18]

In addition, see the Xilinx XPS IIC Bus Interface Data Sheet. [Ref 8]

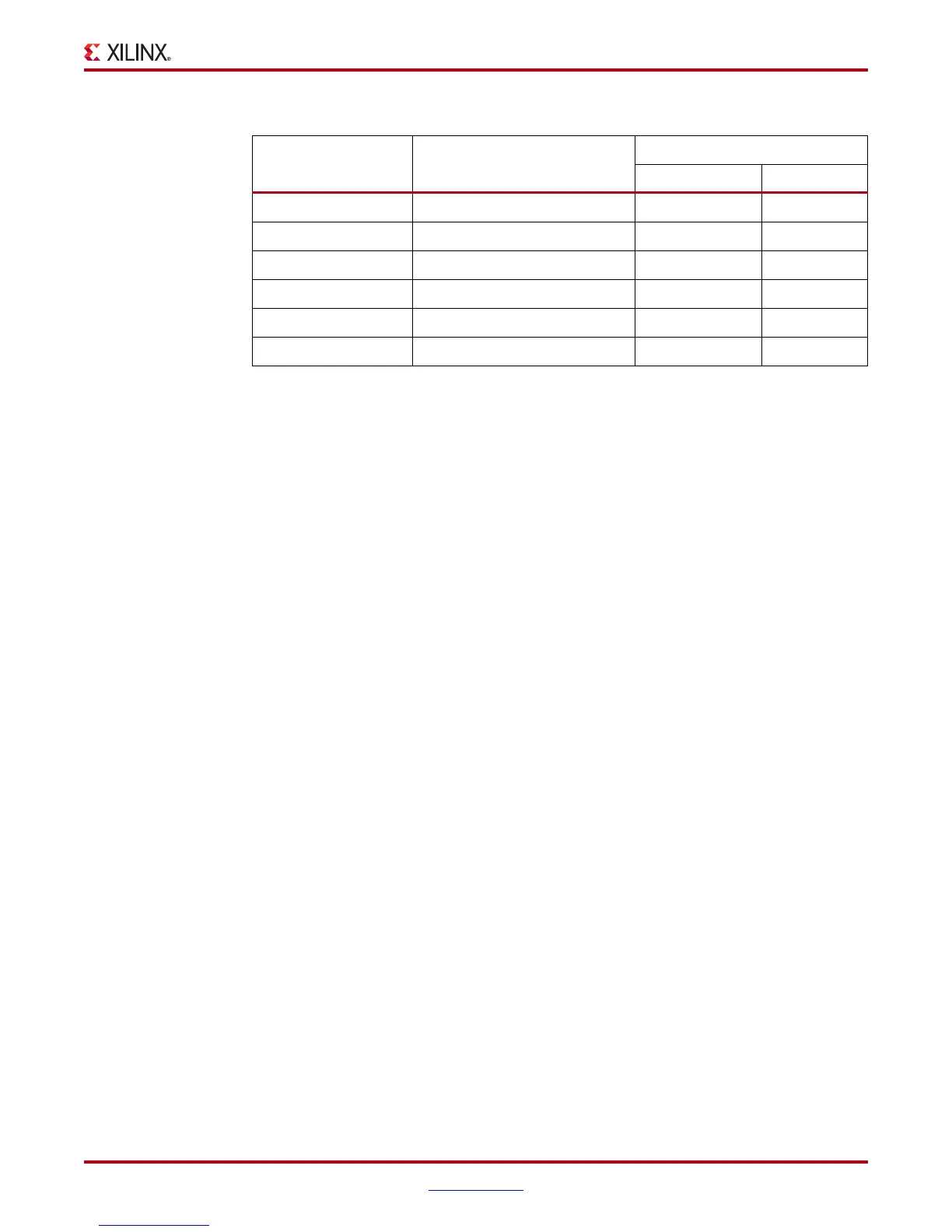

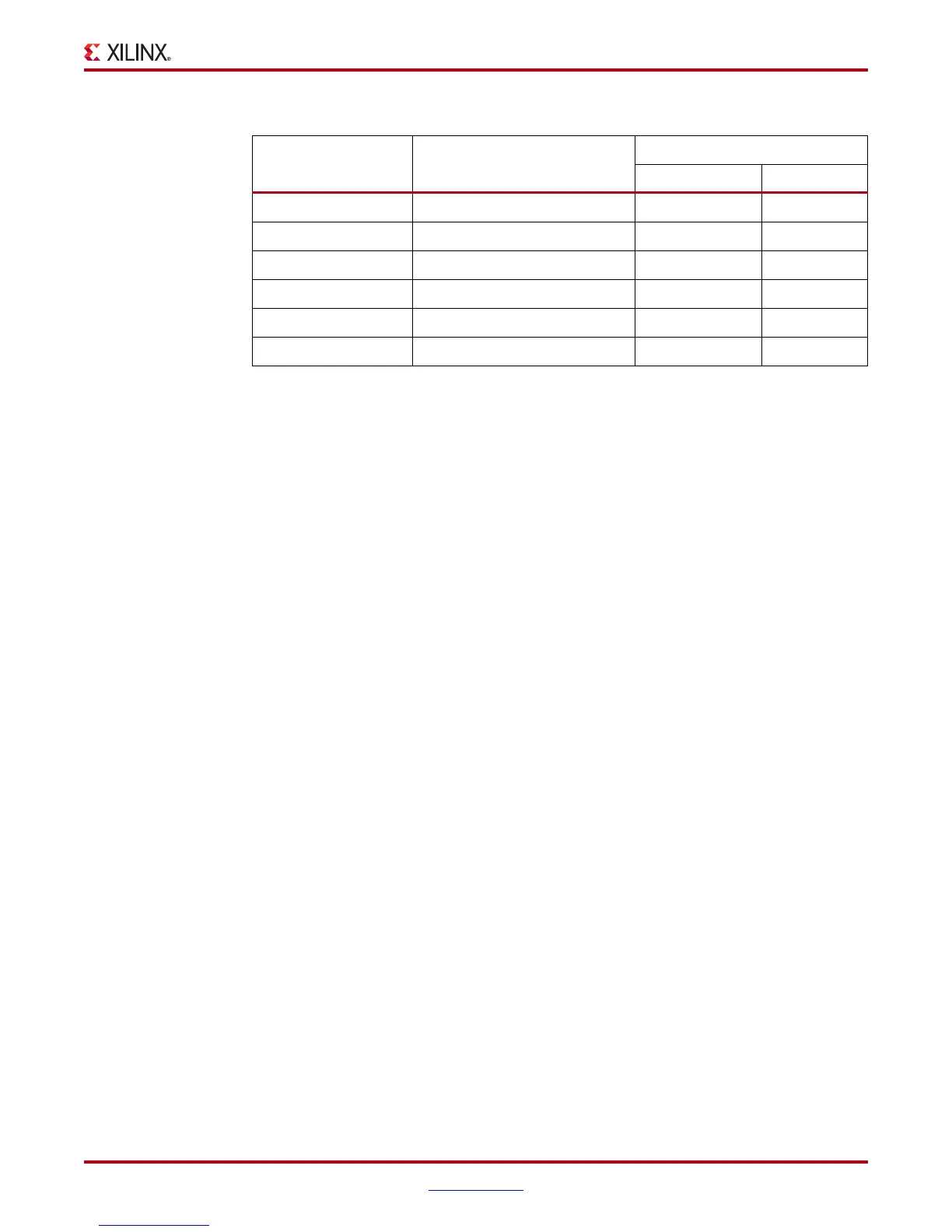

Table 1-20: IIC Memory Connections

U1 FPGA Pin Schematic Netname

IIC Memory U4

Pin Number Pin Name

Not Applicable Tied to GND 1 A0

Not Applicable Tied to GND 2 A1

Not Applicable Pulled up (0 ohm) to VCC3V3 3 A2

R22 IIC_SDA_MAIN 5 SDA

T21 IIC_SCL_MAIN 6 SCL

Not Applicable Tied to GND 7 WP

Loading...

Loading...