VCU1525 Acceleration Platform User Guide 16

UG1268 (v1.0) November 13, 2017 www.xilinx.com

Chapter 3: Board Component Descriptions

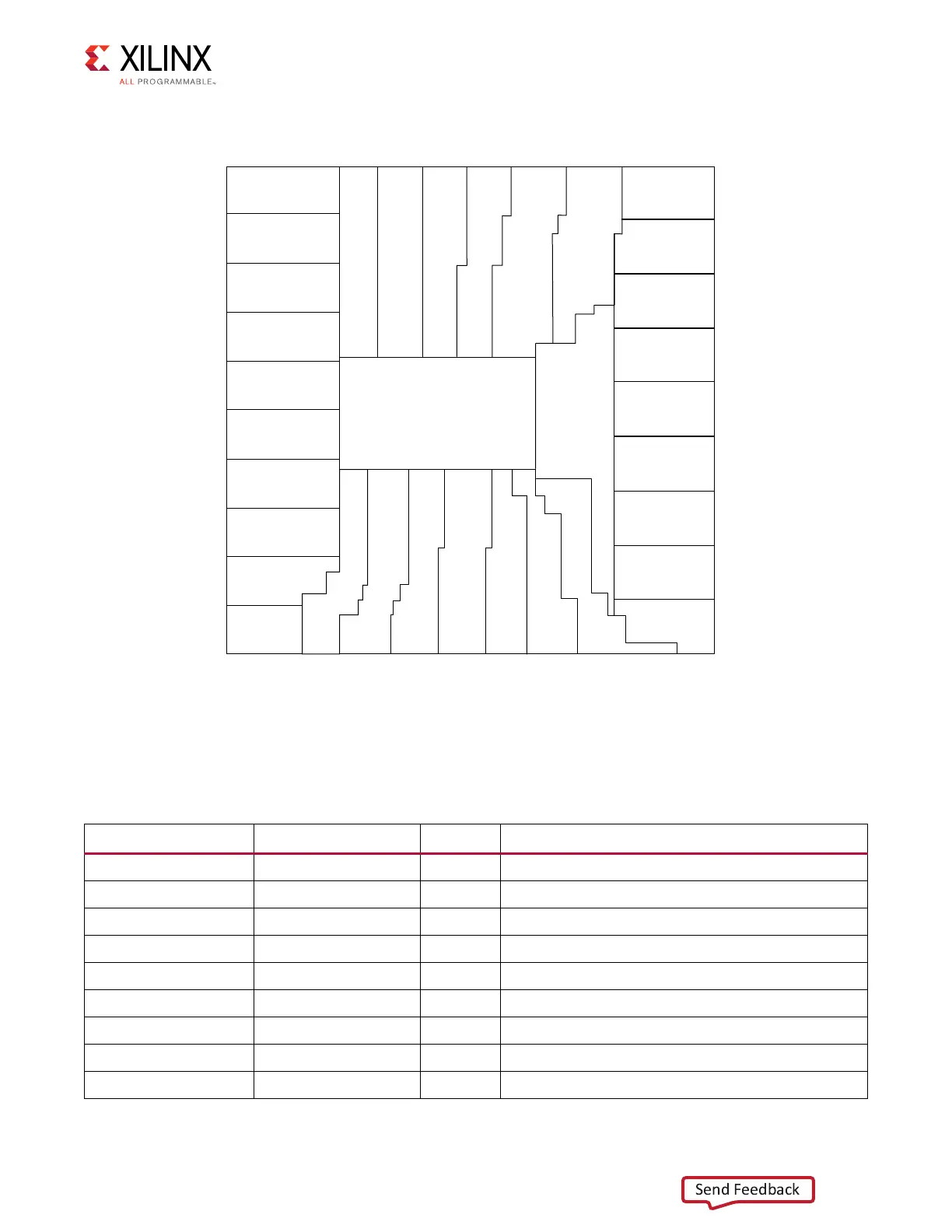

Figure 3-1 shows the XCVU9P-L2FSGD2104E bank arrangement.

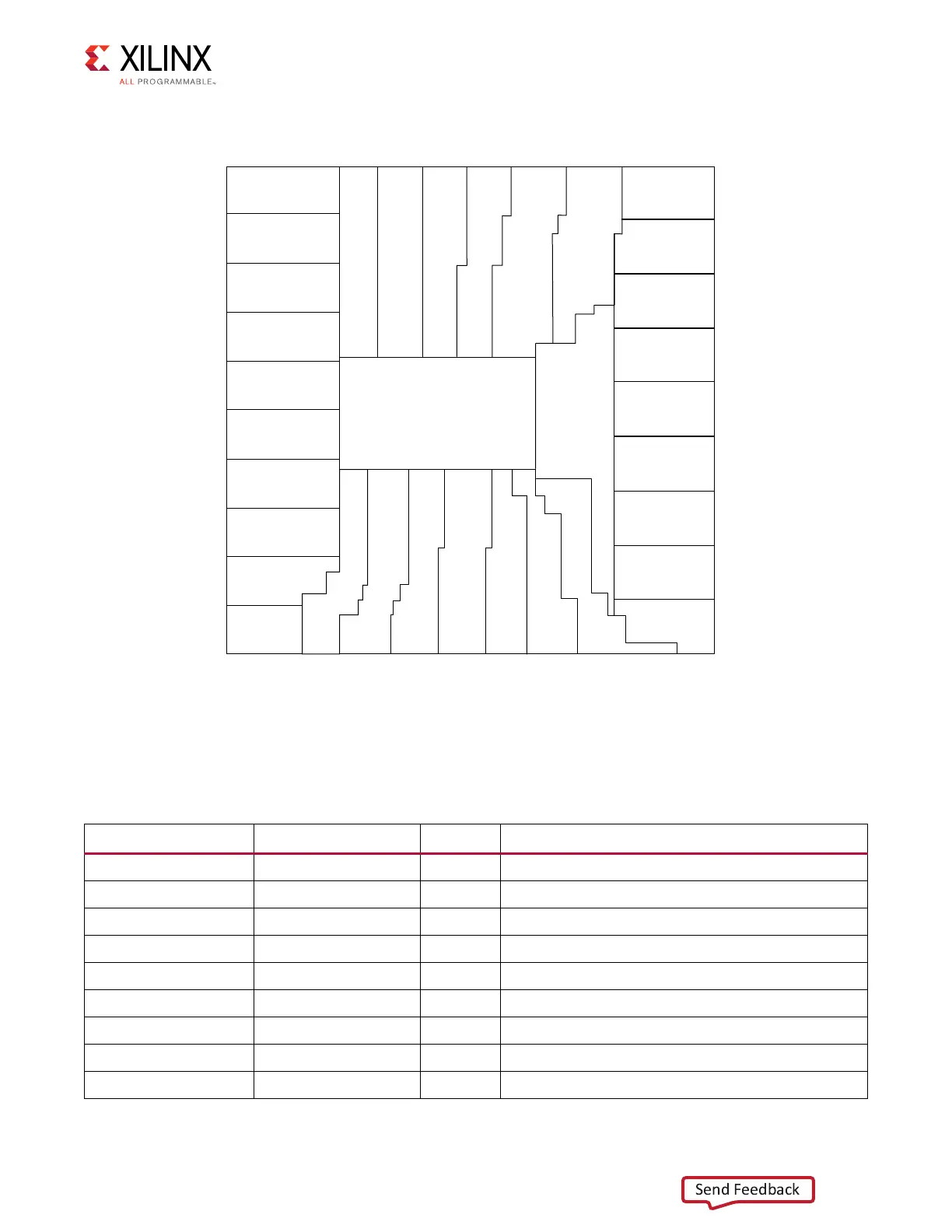

The voltages applied to the XCVU9P-L2FSGD2104E U13 FPGA I/O banks are listed in

Table 3-1.

X-Ref Target - Figure 3-1

Figure 3-1: XCVU9P-L2FSGD2104E Bank Arrangement

MGTY233

MGTY232

MGTY231

MGTY230

MGTY229

MGTY228

MGTY227

MGTY226

MGTY225

MGTY224

MGTY133

MGTY131

MGTY130

MGTY129

MGTY128

MGTY123

MGTY122

MGTY121

MGTY120

72 73 74 71 70 69

66 64 65 61 62 63

67

X19971-103017

Table 3-1: I/O Bank Voltage Rails

XCVU9P-L2FSGD2104E Power Net Name Voltage Connected To

Bank 61 VCC1V2_BTM 1.2V DDR4 C0 DQ[0:15], DQ[40:55]

Bank 62 VCC1V2_BTM 1.2V DDR4 C0 DQ[16:39], DQ[56:63]

Bank 63 VCC1V2_BTM 1.2V DDR4 C0 DQ[64:71], ADDR/CTRL

Bank 64 VCC1V2_BTM 1.2V USB, QSFP0,QSFP1, I2C, GPIO_MSP, SW_DP

Bank 65 VCC1V2_BTM 1.2V DDR4 C1 DQ[64:71], ADDR/CTRL

Bank 66 VCC1V2_BTM 1.2V DDR4 C1 DQ[32:63]

Bank 67 VCC1V8_BTM 1.2V DDR4 C1 DQ[0:31]

Bank 69 VCC1V2_TOP 1.2V DDR4_C2 DQ[32:71]

Bank 70 VCC1V2_TOP 1.2V DDR4 C2 DQ[40:47], ADDR/CTRL

Loading...

Loading...