Zynq UltraScale+ VCU TRD User Guide 43

UG1250 (v2019.1) May 29, 2019 www.xilinx.com

Chapter 3: APU Software Platform

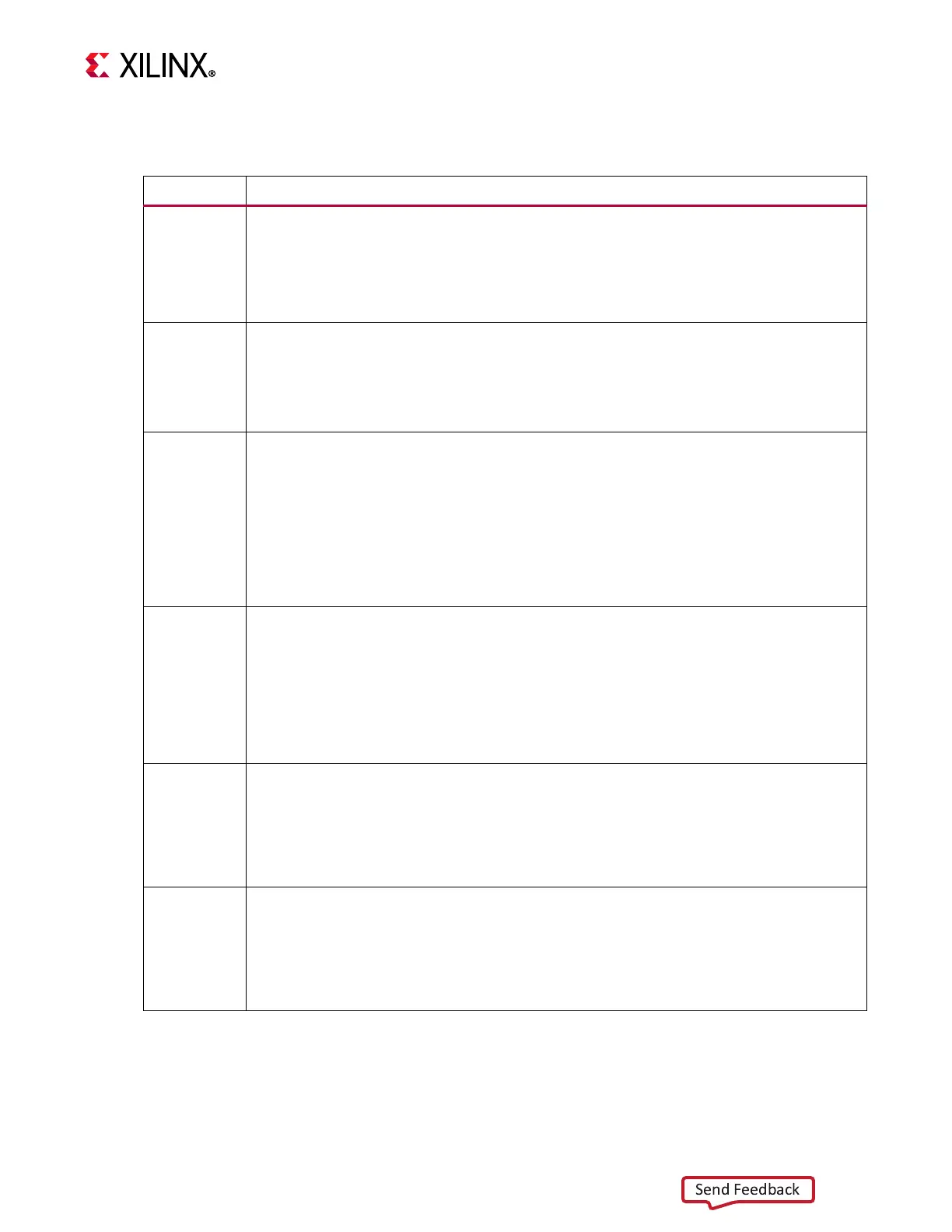

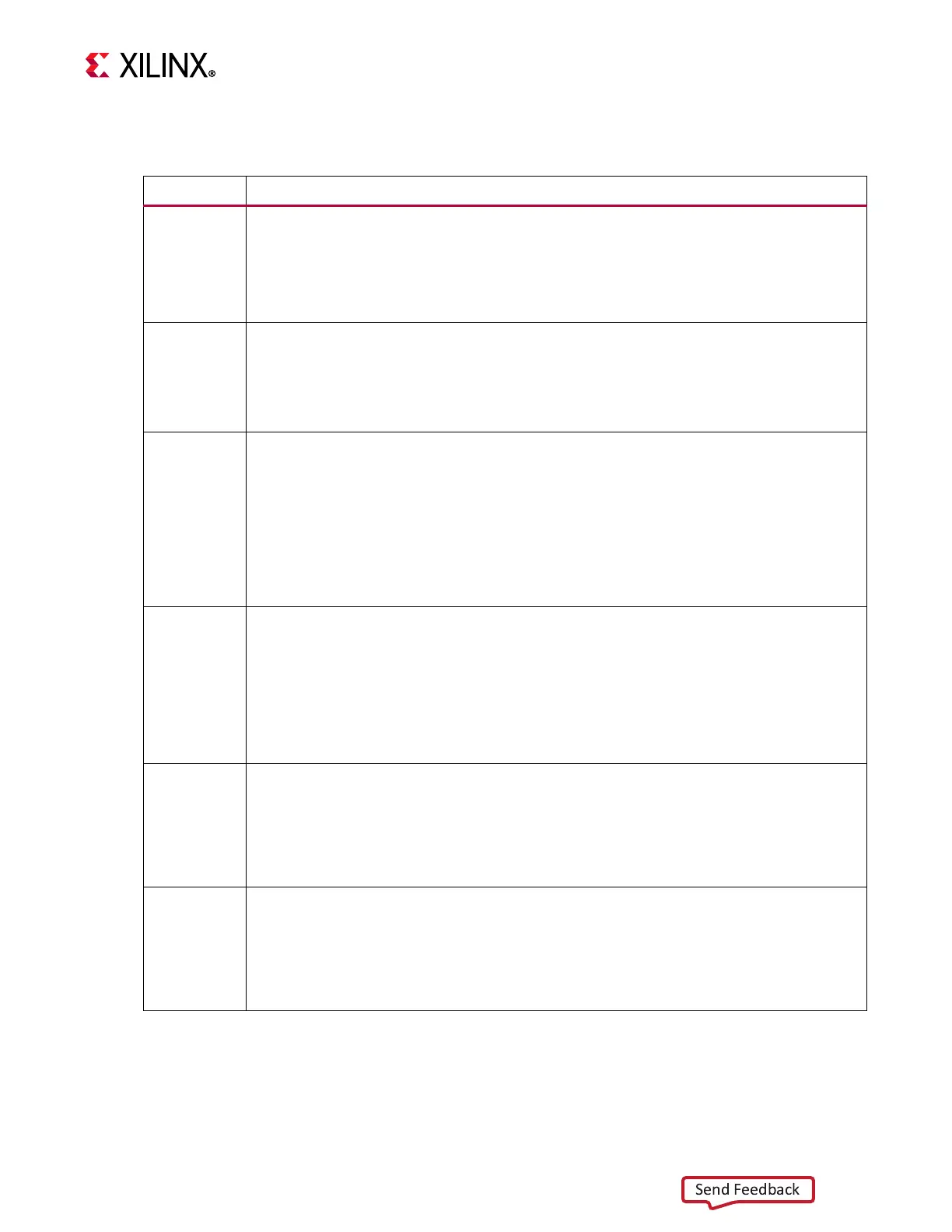

Tab le 3 -7 describes the plug-ins used in the GStreamer interface library.

Table 3-7: GStreamer Plug-ins

Plug-in Description

v4l2src v4l2src can be used to capture video from V4L2 devices like Xilinx HDMI-RX and TPG.

Example pipeline:

gst-launch-1.0 v4l2src ! kmssink

This pipeline shows the video captured from a /dev/video0 and rendered on a display

unit.

kmssink The kmssink is a simple video sink that renders raw video frames directly in a plane of a

DRM device.

Example pipeline:

gst-launch-1.0 v4l2src ! “video/x-raw, format=NV12, width=3840,

height=2160” ! kmssink

omxh26xdec Decoder omxh26xdec is a hardware-accelerated video decoder that decodes encoded

video frames.

Example pipeline:

gst-launch-1.0 filesrc location=/media/card/abc.mp4 ! qtdemux !

h26xparse ! omxh26xdec ! kmssink

This pipeline shows an .mp4 multiplexed file where the encoded format is h26x encoded

video.

Note:

Use omxh264dec for H264 decoding and omxh265dec for H265 decoding.

omxh26xenc Encoder omxh26xenc is a hardware-accelerated video encoder that encodes raw video

frames.

Example pipeline:

gst-launch-1.0 v4l2src ! omxh26xenc ! filesink location=out.h26x

This pipeline shows the video captured from a V4L2 device that delivers raw data. The

data is encoded to the h26x encoded video type and stored to a file.

Note:

Use omxh264enc for H264 encoding and omxh265enc for H265 encoding.

alsasrc The alsasrc plug-in can be used to capture audio from audio devices like Xilinx HDMI-RX.

Example pipeline:

gst-launch-1.0 alsasrc device=hw:1,1 ! queue ! audioconvert !

audioresample ! audio/x-raw, rate=48000, channels=2, format=S24_32LE !

alsasink device="hw:1,0"

This pipeline shows the audio captured from an ALSA source and plays on an ALSA sink.

alsasink The alsasink is a simple audio sink that plays raw audio frames.

Example pipeline:

gst-launch-1.0 alsasrc device=hw:1,1 ! queue ! audioconvert !

audioresample ! audio/x-raw, rate=48000, channels=2, format=S24_32LE !

alsasink device="hw:1,0"

This pipeline shows the audio captured from the ALSA source and plays on an ALSA sink.

Loading...

Loading...