Zynq UltraScale+ VCU TRD User Guide 60

UG1250 (v2019.1) May 29, 2019 www.xilinx.com

Chapter 5: Hardware Platform

AXI4-Stream output interface. For more information, see the HDMI 1.4/2.0 Receiver

Subsystem Product Guide (PG236) [Ref 12].

• The Video Processing Subsystem (VPSS) is a collection of video processing IP subcores.

In this design, the VPSS uses the Video Scaler only configuration which provides

scaling, color space conversion, and chroma resampling functionality. The VPSS takes

AXI4-Stream input data from the HDMI RX Subsystem and depending on the input

format and resolution, converts and scales it to the desired output format and

resolution again using AXI4-Stream. A GPIO is used to reset the subsystem between

resolution changes. For more information, see the Video Processing Subsystem Product

Guide (PG231) [Ref 13].

• The Video Frame Buffer Write IP uses the same configuration as the one in the TPG

capture pipeline. It takes AXI4-Stream input data from the VPSS and converts it to

memory-mapped AXI4 format. The output is connected to the HP1 high performance

PS/PL interface via an AXI interconnect. For each video frame transfer, an interrupt is

generated. A GPIO is used to reset the IP between resolution changes.

Similar to the TPG pipeline, the HDMI RX, VPSS Video Scaler, and Frame Buffer Write IPs are

configured to transport two pixels per clock (ppc), enabling up to 2160p60 performance.

Although the color format and depth at the HDMI RX are determined by the HDMI source,

the VPSS always converts the format to YUV 4:2:0, 8 bits per component (bpc), which is then

written to memory by the Frame Buffer Write IP as NV12 format.

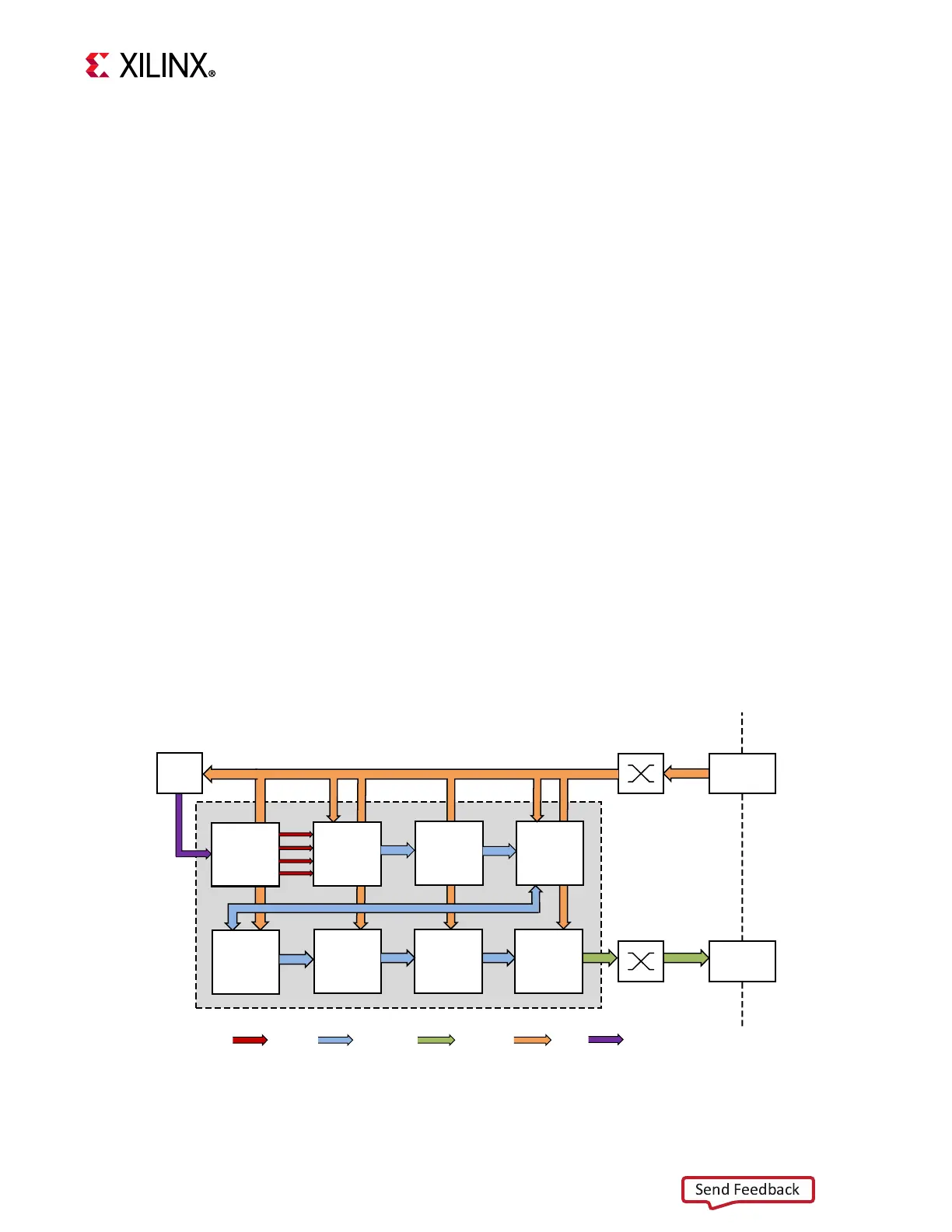

MIPI CSI-2 RX Capture Pipeline

The MIPI CSI-2 receiver capture pipeline is shown in Figure 5-5.

X-Ref Target - Figure 5-5

Figure 5-5: CSI Video Capture Pipeline

32

1283248

Frmbuf

Write

CSI data AXI-S AXI-MM

HP1

HPM0/1

AXI-Lite

PL

PS

HP1

VPSS

CSC

VPSS

Scaler

MIPI CSI-2

Rx SS

MIPI CSI-2 Rx Capture Pipeline

48

32

AXI-S

Subset

Converter

Demosaic

20

24

Gamma

48

IMX274

Sensor

48

AXI

I2C

I2C

X20150-042519

Loading...

Loading...