PCIE-1816_1816H User Manual 40

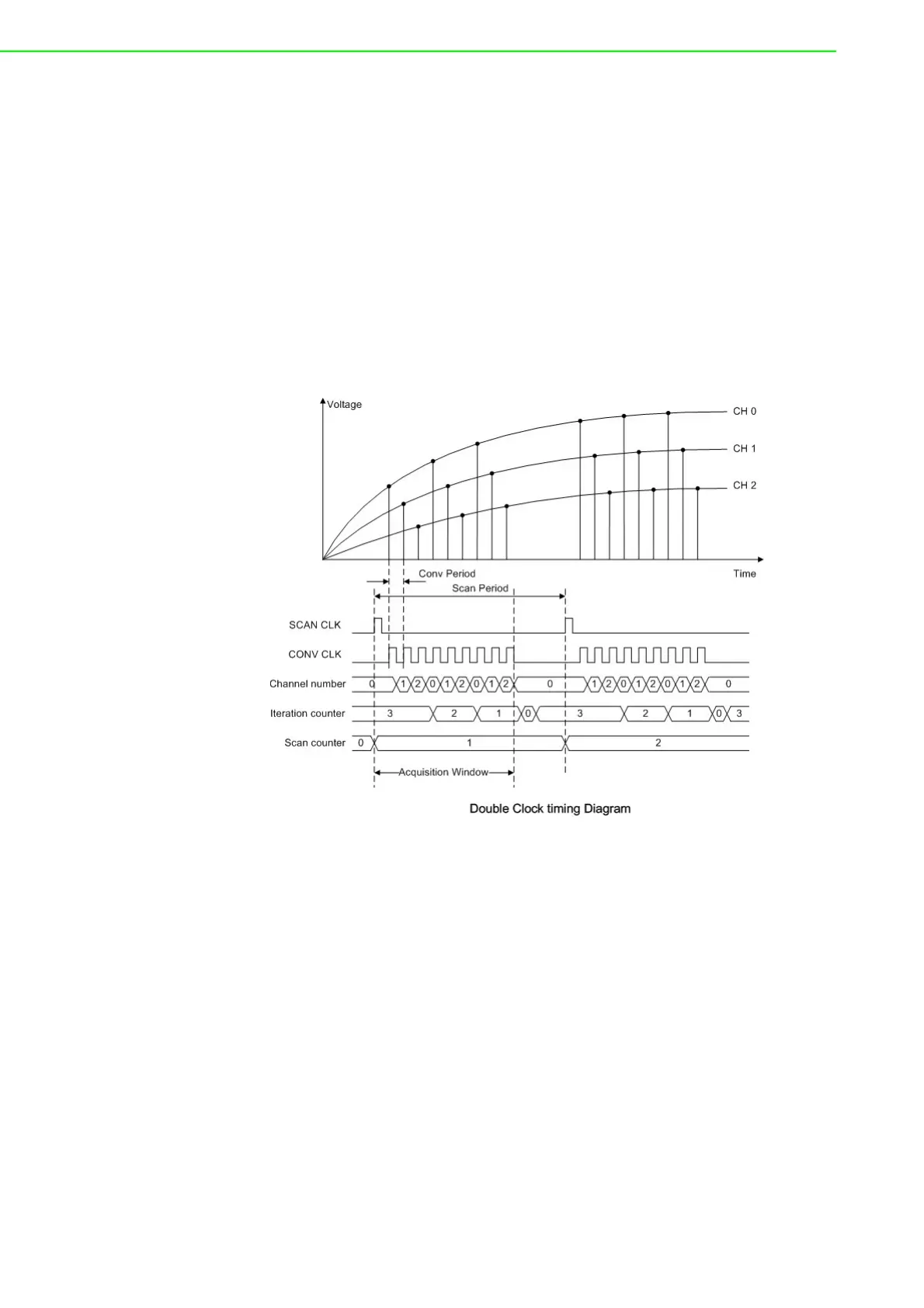

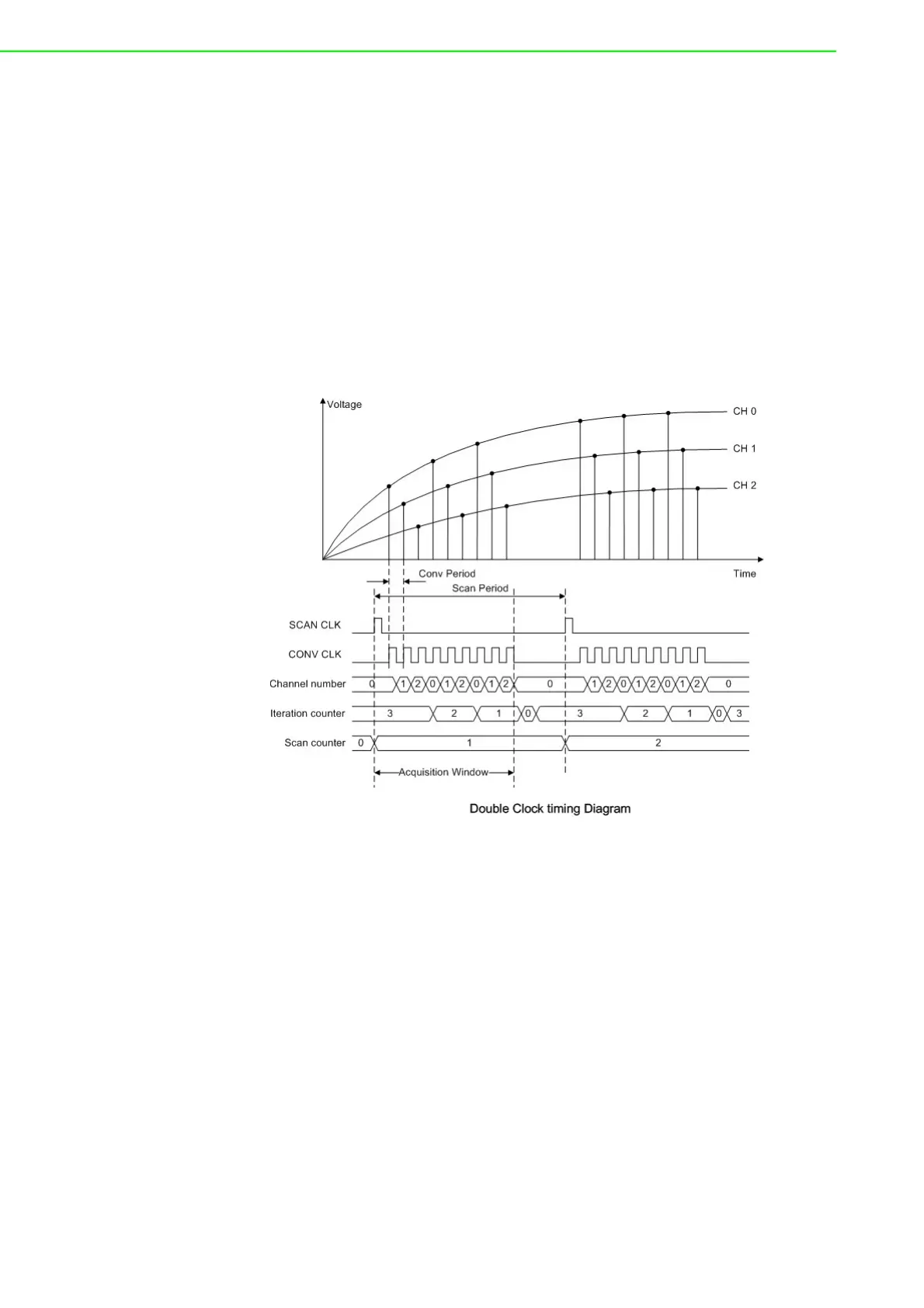

Double-Clock Procedure

Double clock procedure is the fundamental AI conversion mechanism of the PCIE-

1816/1816H, regardless of which mode selected. The incoming SCAN CLK launches

an acquisition period called Acquisition Window. The arriving CONV CLKs within the

Acquisition Window will become an efficient AI conversion clock to trigger AI con-

verter. The number of efficient CONV CLK depends on the number of active scan-

ning (multiplex) channels and software-programed iteration counters. One scanning

iteration is defined as the time auto-scan multiplexer routes input channels from Start

channel to Stop channel once. On the other words, all the active channels are sam-

pled once in a single iteration. After the iteration counter counts down to zero, the

Acquisition Window will be disable automatically and wait for the next incoming

SCAN CLK. The end of Acquisition Window resets the iteration counter to its user-

specified value. Users can specify the iteration counter by software and read back

the number of incoming SCAN CLKs from SCAN CLK counter.

Once the acquisition procedure inside Acquisition Windows is set, the incoming

CLKs must fit in the user-specified acquisition sequence, or the CLKs may be gated

off. Refer to the following figures for more details.

Loading...

Loading...