47 PCIE-1816_1816H User Manual

Appendix B Operation Theory

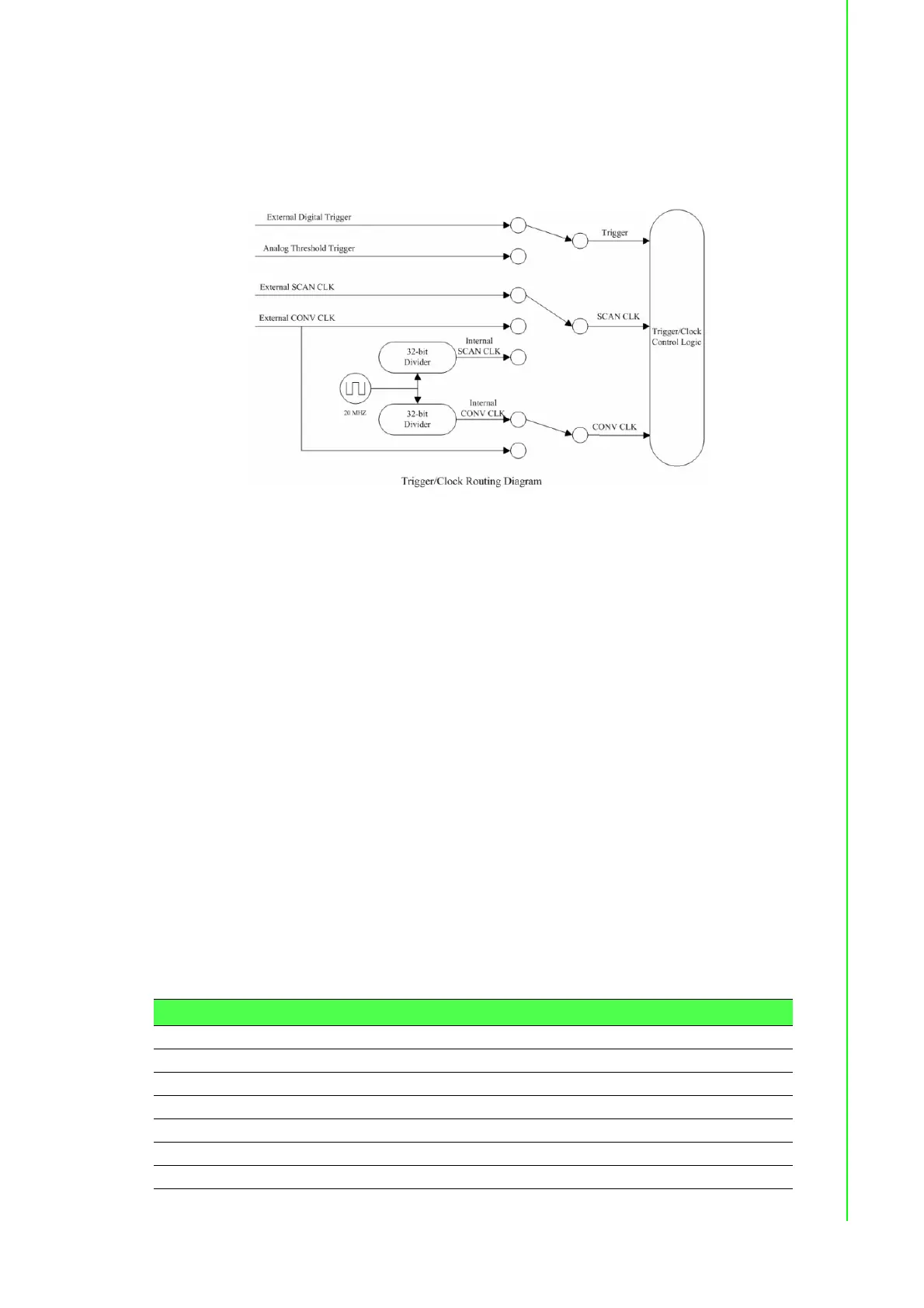

External AI CONV Clock

The external AI CONV Clock is convenient in uneven sampling internal. AI conver-

sion will start by each arriving rising edge. The sampling frequency is always limited

to a maximum of 500 KHz.

B.1.6 AI Trigger Source

The PCIE-1816/1816H supports the following trigger sources for start, delay to start,

delay to stop, stop trigger acquisition modes:

External digital (TTL) trigger

Analog threshold trigger

With PCIE-1816/1816H, user can also define the type of trigger source as rising-

edge or falling-edge. These following sections describe these trigger sources in more

detail.

External Digital (TTL) Trigger

For analog input operations, an external digital trigger event occurs when the PCIE-

1816/1816H detects either a rising or falling edge on the External AI TTL trigger

input. The trigger signal is TTL compatible.

Analog Threshold Trigger

For analog input operations, an analog trigger event occurs when the PCIE-1816/

1816H detects a transition from above a threshold level to below a threshold level

(falling edge), or a transition from below a threshold level to above a threshold level

(rising edge). User should connect analog signals from external device or analog out-

put channel on board to external input signal ATRG0/1. On the PCIE-1816/1816H,

the threshold level is set using a dedicated 16-bit DAC. By software, you can pro-

gram the threshold level by writing a voltage value to this DAC; this value can range

from -10 V to +10 V.

Table B.2: Analog Input Data Format

AI Code Mapping Voltage

Hex. Dec. Unipolar Bipolar

0000 h 0 d 0 - FS/2

7FFF h 32767 d FS/2 - 1 LSB - 1LSB

8000 h 32768 d FS/2 0

FFFF h 65535 d FS - 1 LSB FS/2 - 1 LSB

1 LSB FS/65536 FS/65536

Loading...

Loading...