3. Phase Comparator The PLL (IC102) uses the reference frequency, 5 or 6.25 kHz. The phase

Circuit comparator in the IC102 compares the phase of the frequency from the

VCO with that of the comparison frequency, 5 or 6.25 kHz, which is

obtained by the internal divider in IC102.

4. PLL Loop Filter Circuit If a phase difference is found in the phase comparison between the

reference frequency and VCO output frequency, the charge pump output

(pin 8) of IC102 generates a pulse signal, which is converted to DC voltage

by the PLL loop filter and input to the varicap of the VCO unit for oscillation

frequency control.

5, VC O C ircuit A Colpitts oscillation circuit driven by Q301 directly oscillates the desired

frequency. The frequency control voltage determined in the CPU (IC5) and

PLL circuit is input to the varicaps (D301 and D304). This changes the

oscillation frequency, which is amplified by the VCO buffer (Q302) and

output from the VCO unit.

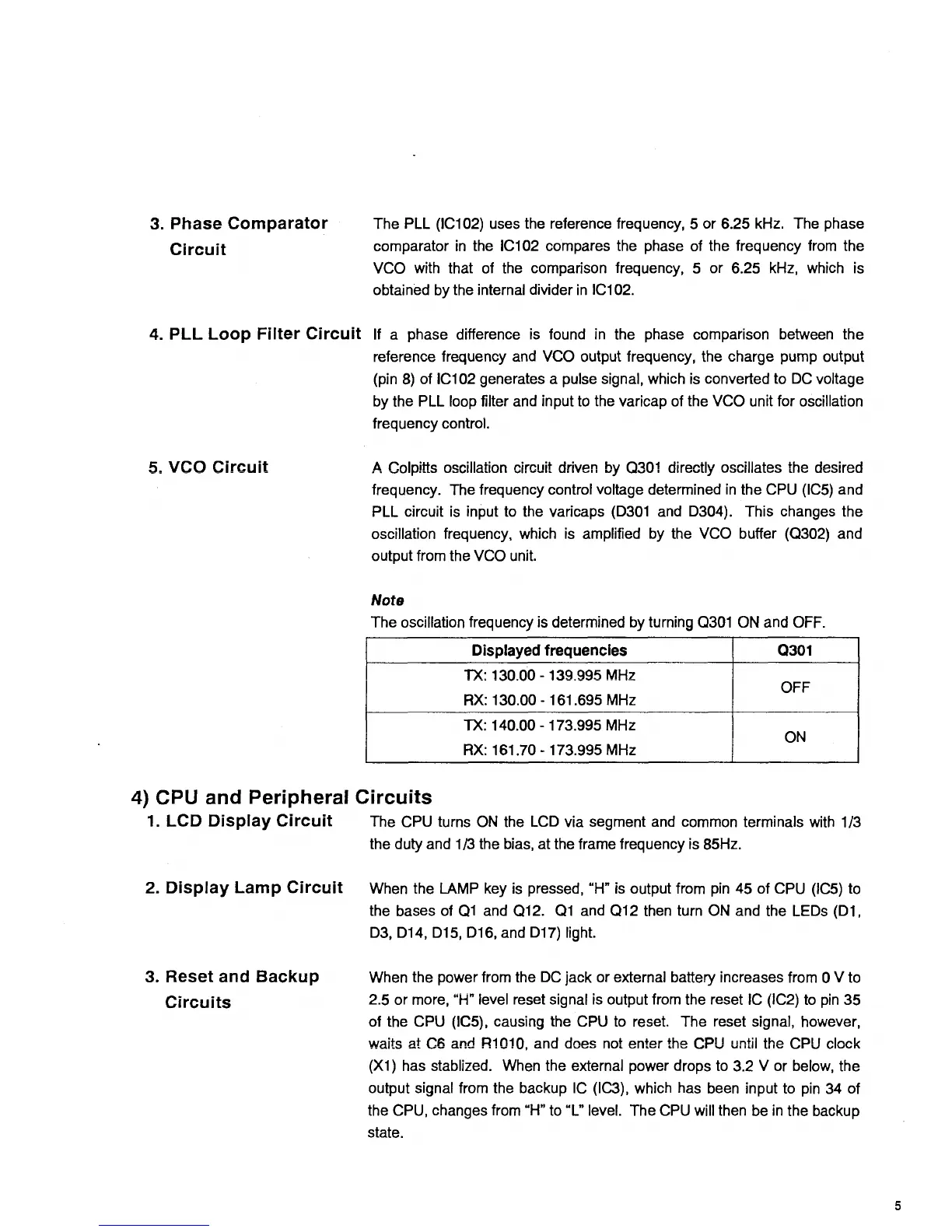

Note

The oscillation frequency is determined by turning Q301 ON and OFF.

Displayed frequencies

Q301

TX: 130.00 -139.995 MHz

RX: 130.00- 161.695 MHz

OFF

TX: 140.00-173.995 MHz

RX: 161.70- 173.995 MHz

ON

4) CPU and Peripheral Circuits

1. LCD Display Circuit The CPU turns ON the LCD via segment and common terminals with 1/3

the duty and 1/3 the bias, at the frame frequency is 85Hz.

2. Display Lamp Circuit

When the LAMP key is pressed, “H” is output from pin 45 of CPU (IC5) to

the bases of Q1 and Q12. Q1 and Q12 then turn ON and the LEDs (D1,

D3, D14, D15, D16, and D17) light.

3. Reset and Backup

Circuits

When the power from the DC jack or external battery increases from 0 V to

2.5 or more, “H” level reset signal is output from the reset IC (IC2) to pin 35

of the CPU (IC5), causing the CPU to reset. The reset signal, however,

waits at C6 and R1Q10, and does not enter the CPU until the CPU clock

(X1) has stablized. When the external power drops to 3.2 V or below, the

output signal from the backup IC (IC3), which has been input to pin 34 of

the CPU, changes from “H” to “L” level. The CPU will then be in the backup

state.

5

Loading...

Loading...