UG-1098 ADE9000 Technical Reference Manual

Rev. 0 | Page 62 of 86

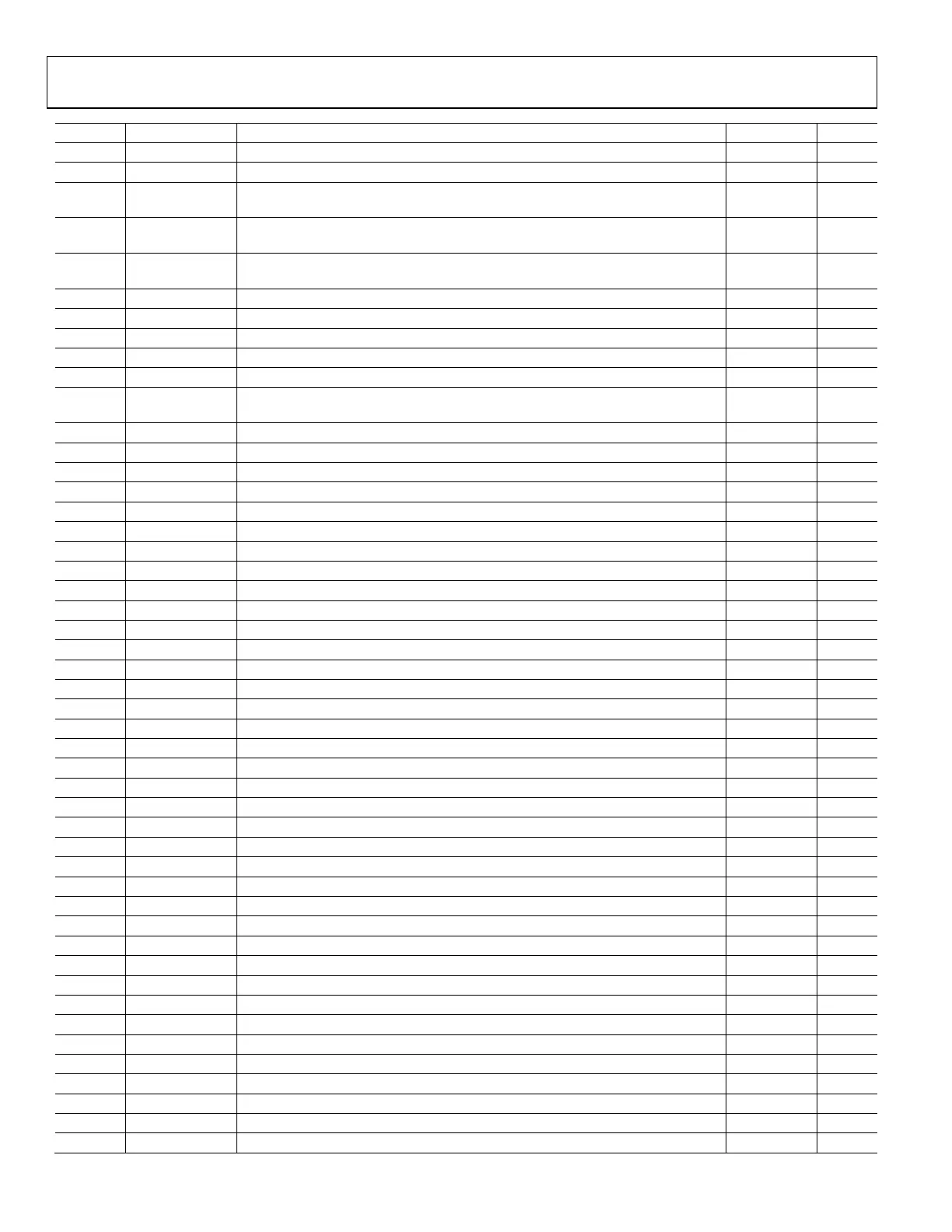

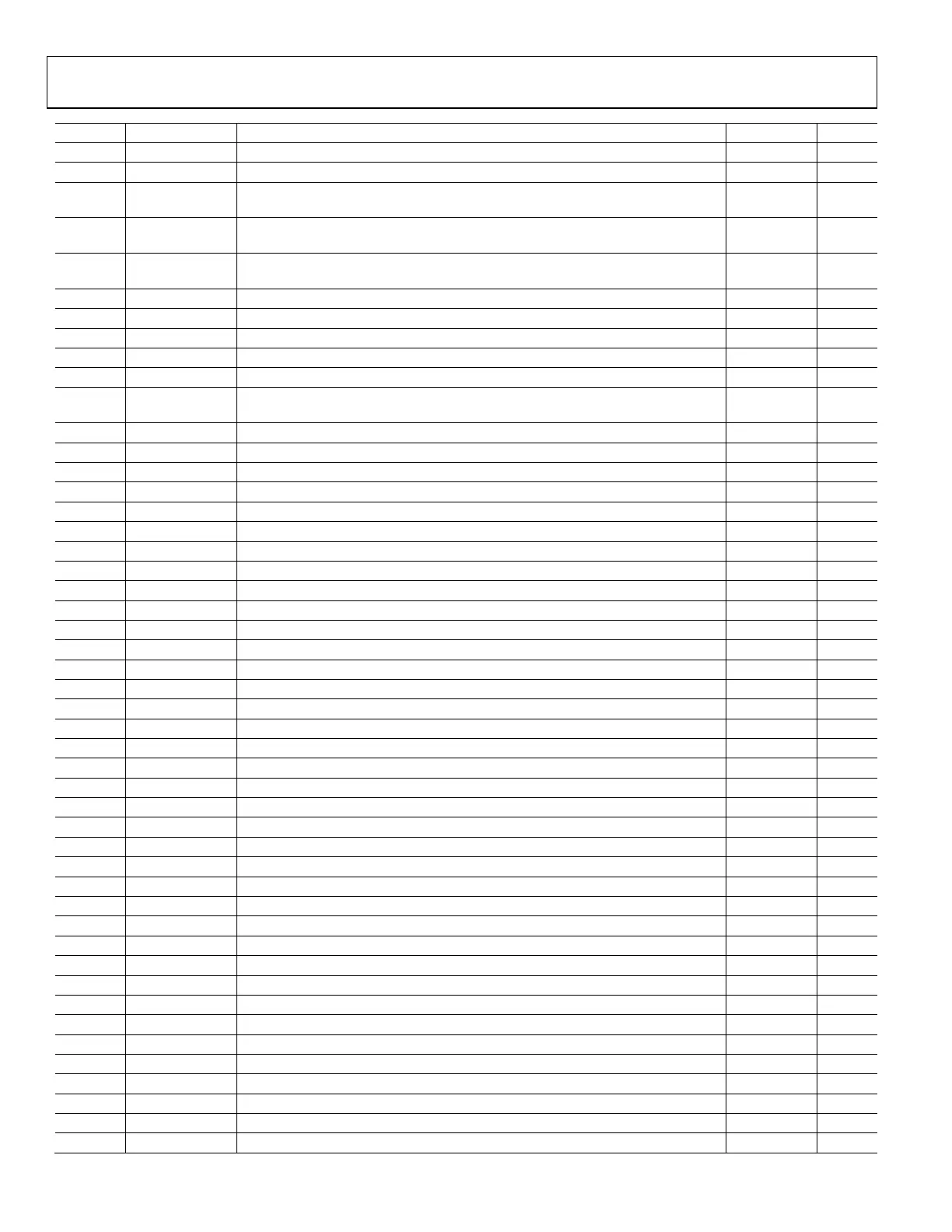

Address Name Description Reset Access

Configuration Register 5.

0x4A8 CRC_RSLT This register holds the CRC of the configuration registers. 0x0000 R

0x4A9 CRC_SPI This register holds the 16-bit CRC of the data sent out on the MOSI pin during the

last SPI register read.

0x0000 R

0x4AC LAST_DATA_16 This register holds the data read or written during the last 16-bit transaction on

the SPI port.

0x0000 R

0x4AE LAST_CMD This register holds the address and read/write operation request (CMD_HDR) for

the last transaction on the SPI port.

0x0000 R

Configuration Register 2.

0x4B0 EP_CFG Energy and power accumulation configuration. 0x0000 R/W

0x4B1 PWR_TIME Power update time configuration. 0x00FF R/W

Energy accumulation update time configuration.

0x4B4 CRC_FORCE This register forces an update of the CRC of configuration registers. 0x0000 R/W

0x4B5 CRC_OPTEN This register selects which registers are optionally included in the configuration

register CRC feature.

0x0000 R/W

0x4B6 TEMP_CFG Temperature sensor configuration register. 0x0000 R/W

0x4B7 TEMP_RSLT Temperature measurement result. 0x0000 R

0x4B9 PGA_GAIN This register configures the PGA gain for each ADC. 0x0000 R/W

0x4BA CHNL_DIS ADC channel enable/disable. 0x0000 R/W

0x4BF WR_LOCK This register enables the configuration lock feature. 0x0000 R/W

0x4E0 VAR_DIS Enables/disables total reactive power calculation. 0x0000 R/W

0x4F0 RESERVED1 This register is reserved. 0x0000 R

0x4FE Version Version of ADE9000 IC. 0x0040 R

0x500 AI_SINC_DAT Current channel A ADC waveforms from the sinc4 output at 32 kSPS. 0x00000000 R

0x501 AV_SINC_DAT Voltage channel A ADC waveforms from the sinc4 output at 32 kSPS. 0x00000000 R

0x502 BI_SINC_DAT Current channel B ADC waveforms from the sinc4 output at 32 kSPS. 0x00000000 R

0x503 BV_SINC_DAT Voltage channel B ADC waveforms from the sinc4 output at 32 kSPS. 0x00000000 R

0x504 CI_SINC_DAT Current channel C ADC waveforms from the sinc4 output at 32 kSPS. 0x00000000 R

Voltage channel C ADC waveforms from the sinc4 output at 32 kSPS.

0x506 NI_SINC_DAT Neutral current channel ADC waveforms from the sinc4 output at 32 kSPS. 0x00000000 R

0x510 AI_LPF_DAT Current channel A ADC waveforms from the sinc4 + IIR LPF output at 8 kSPS. 0x00000000 R

0x511 AV_LPF_DAT Voltage channel A ADC waveforms from the sinc4 + IIR LPF output at 8 kSPS. 0x00000000 R

0x512 BI_LPF_DAT Current channel B ADC waveforms from the sinc4 + IIR LPF output at 8 kSPS. 0x00000000 R

0x513 BV_LPF_DAT Voltage channel B ADC waveforms from the sinc4 + IIR LPF output at 8 kSPS. 0x00000000 R

0x514 CI_LPF_DAT Current channel C ADC waveforms from the sinc4 + IIR LPF output at 8 kSPS. 0x00000000 R

0x515 CV_LPF_DAT Voltage channel C ADC waveforms from the sinc4 + IIR LPF output at 8 kSPS. 0x00000000 R

0x516 NI_LPF_DAT Neutral current channel ADC waveforms from the sinc4 + IIR LPF output at 8 kSPS. 0x00000000 R

0x600 AV_PCF_1 SPI burst read accessible. Registers organized functionally. See AV_PCF. 0x00000000 R/W

SPI burst read accessible. Registers organized functionally. See BV_PCF.

0x602 CV_PCF_1 SPI burst read accessible. Registers organized functionally. See CV_PCF. 0x00000000 R/W

0x603 NI_PCF_1 SPI burst read accessible. Registers organized functionally. See NI_PCF. 0x00000000 R/W

0x604 AI_PCF_1 SPI burst read accessible. Registers organized functionally. See AI_PCF. 0x00000000 R/W

0x605 BI_PCF_1 SPI burst read accessible. Registers organized functionally. See BI_PCF. 0x00000000 R/W

0x606 CI_PCF_1 SPI burst read accessible. Registers organized functionally. See CI_PCF. 0x00000000 R/W

0x607 AIRMS_1 SPI burst read accessible. Registers organized functionally. See AIRMS. 0x00000000 R/W

0x608 BIRMS_1 SPI burst read accessible. Registers organized functionally. See BIRMS. 0x00000000 R/W

0x609 CIRMS_1 SPI burst read accessible. Registers organized functionally. See CIRMS. 0x00000000 R/W

0x60A AVRMS_1 SPI burst read accessible. Registers organized functionally. See AVRMS. 0x00000000 R/W

0x60B BVRMS_1 SPI burst read accessible. Registers organized functionally. See BVRMS. 0x00000000 R/W

0x60C CVRMS_1 SPI burst read accessible. Registers organized functionally. See CVRMS. 0x00000000 R/W

0x60D NIRMS_1 SPI burst read accessible. Registers organized functionally. See NIRMS. 0x00000000 R/W

0x60E AWAT T_1 SPI burst read accessible. Registers organized functionally. See AWATT. 0x00000000 R/W

Loading...

Loading...