UG-1098 ADE9000 Technical Reference Manual

Rev. 0 | Page 78 of 86

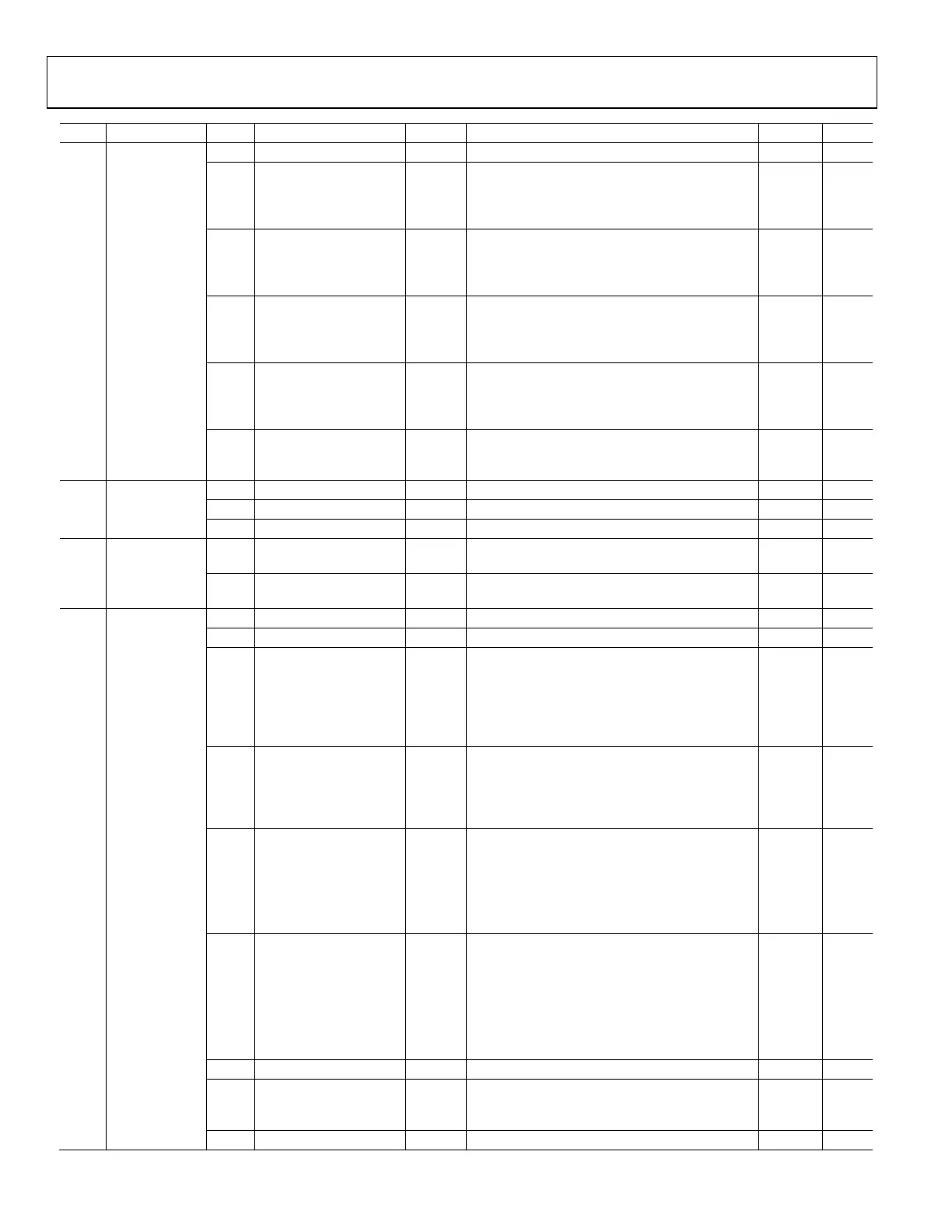

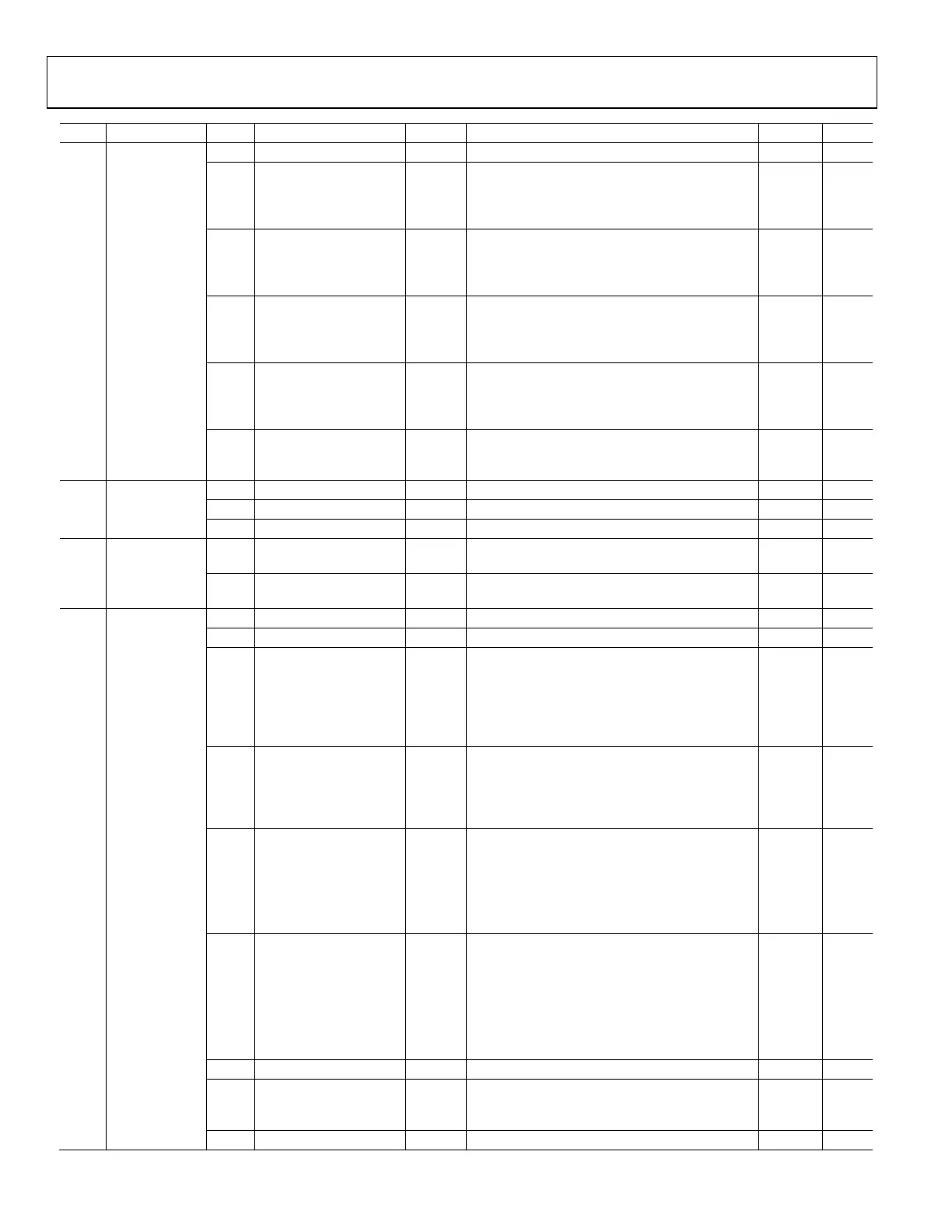

Addr. Name Bits Bit Name Settings Description Reset Access

0x425 CF_LCFG [31:23] RESERVED Reserved. 0x0 R

22 CF4_LT If this bit is set, the CF4 pulse width is determined

by the CF_LTMR register value. If this bit is equal

to zero, then the active low pulse width is set at

80 ms for frequencies lower than 6.25 Hz.

0x0 R/W

21 CF3_LT If this bit is set, the CF3 pulse width is determined

by the CF_LTMR register value. If this bit is equal

to zero, the active low pulse width is set at 80 ms

for frequencies lower than 6.25 Hz.

0x0 R/W

20 CF2_LT If this bit is set, the CF2 pulse width is determined

by the CF_LTMR register value. If this bit is equal

to zero, the active low pulse width is set at 80 ms

for frequencies lower than 6.25 Hz.

0x0 R/W

If this bit is set, the CF1 pulse width is determined

by the CF_LTMR register value. If this bit is equal

to zero, the active low pulse width is set at 80 ms

for frequencies lower than 6.25 Hz.

[18:0] CF_LTMR If the CFx_LT bit in the CF_LCFG register is set,

this value determines the active low pulse width

of the CFx pulse.

0x0 R/W

0x472 PART_ID [31:21] RESERVED Reserved. 0x0 R

20 ADE9000_ID This bit is set to identify an ADE9000 IC. 0x1 R

[19:0] RESERVED Reserved. 0x0 R

0x474 TEMP_TRIM [31:16] TEMP_OFFSET Offset of temperature sensor, calculated during

the manufacturing process.

0x0 R/W

[15:0] TEMP_GAIN Gain of temperature sensor, calculated during

the manufacturing process.

0x0 R/W

0x481 CONFIG1 15 EXT_REF Set this bit if using an external voltage reference. 0x0 R/W

[14:13] RESERVED Reserved. 0x0 R

12 IRQ0_ON_IRQ1 Set this bit to combine all the interrupts onto a

single interrupt pin, IRQ1, instead of using two

pins, IRQ0 and IRQ1. Note that the IRQ0 pin still

indicates the enabled IRQ0 events while in this

mode and the IRQ1pin indicates both IRQ1 and

IRQ0 events.

0x0 R/W

11 BURST_EN Set this bit to enable burst read functionality on

the registers from Address 0x500 to Address 0x63C

or Address 0x680 to Address 0x6BC. Note that this

bit disables the CRC being appended to SPI

register reads.

0x0 R/W

10 DIP_SWELL_IRQ_MODE Set interrupt mode for dip/swell. 0x0 R/W

0 Receive continuous interrupts after every

DIP_CYC/SWELL_CYC cycles.

1 Receive one interrupt when entering dip/swell

mode and another interrupt when exiting

dip/swell mode.

These bits configure the time for the power and

filter-based rms measurements to settle before

starting the power, energy, and CF accumulations.

0: 64 ms.

1: 128 ms.

2: 256 ms.

3: 0 ms.

[7:6] RESERVED Reserved. 0x0 R

5 CF_ACC_CLR Set this bit to clear the accumulation in the digital

to frequency converter and the CFDEN counter.

Note that this bit automatically clears itself.

0x0 W

4 RESERVED Reserved. 0x0 R

Loading...

Loading...