4 Reset Generation 31

CW6632B Bluetooth 3.0 Audio Player SOC Version 1.0.0

Copyright ©2015, www.appotech.com. All Rights Reserved.

0 = Enable

1 = Disable

RCEN: RC enable bit

0 = Disable

1 = Enable

SYS_PLL_SEL: system PLL clock select

0 = PLL1 48MHz

1 = PLL2 49.152 MHz

Register 4-6 CLKCON – Clock control

RCSEL: RC frequency select

00 = RC 512K

01 = RC 32K

10 = RC 1M

11 = RC 4M or XOSC26M controlled by CLKCON2[3]

WDTCSEL: WDT clock section

0 = Internal 32 KHz RC oscillator output

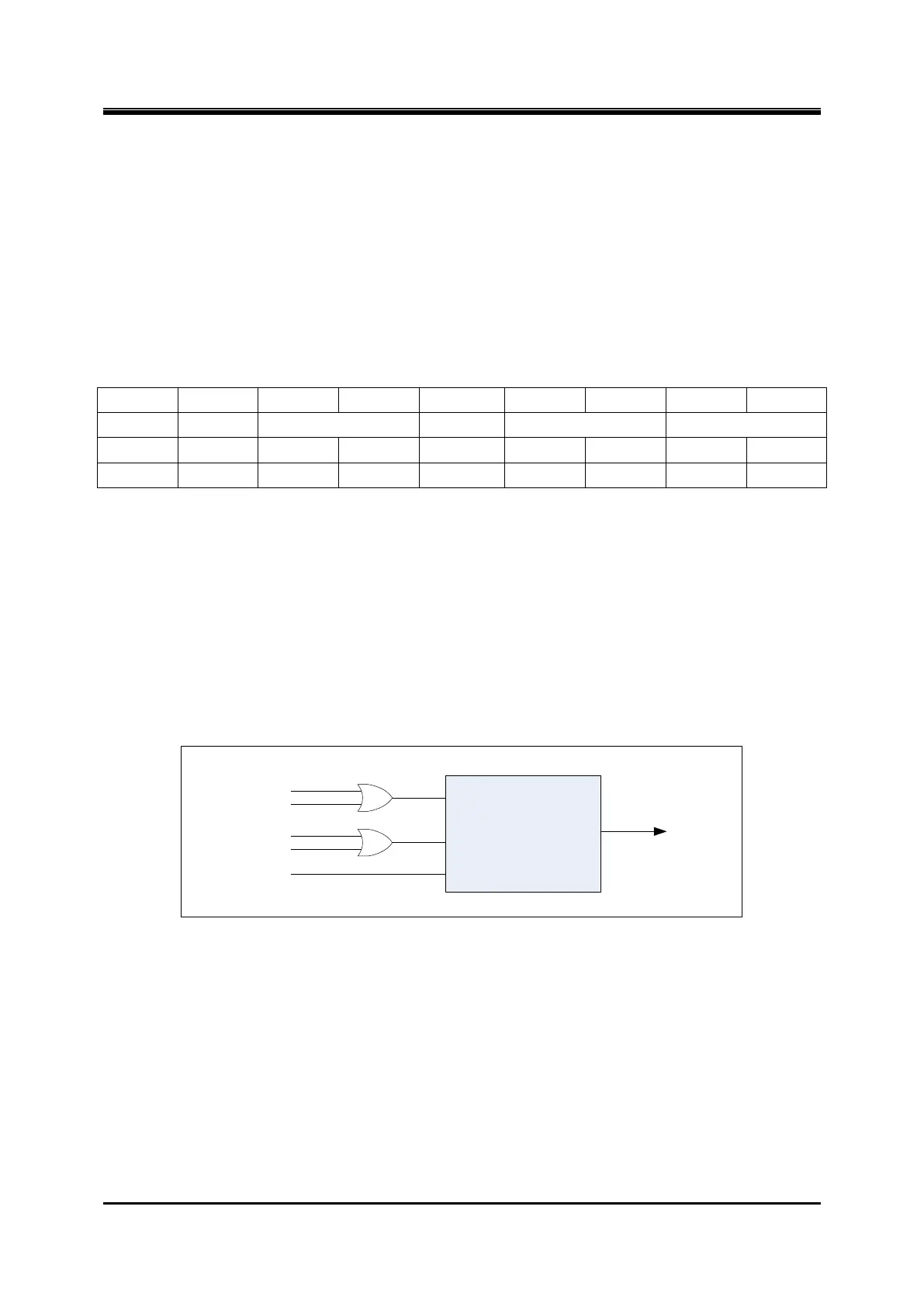

1 = External 32 KHz or 12MHz crystal oscillator controlled by CLKCON2 [6] and CLKCON2 [7] as shown in XFigure

4-3

XOSC

XCK12V

OR

RTC_CFG.6

CLKCON2.6

X12MEN

OR

RTC_CFG.7

CLKCON2.7

X32KEN

RTC_CFG.5

Figure 4-3 Source of XCK12V

RTCCS: RTCC clock source select

00 = External 32 KHz or 12MHz crystal oscillator controlled by CLKCON2 [6] and CLKCON2 [7] as shown in Figure

4-3

01 = Internal 32 KHz RC oscillator output

10 = Select 32 KHz clock source derived from external 12MHz crystal oscillator

11 = Reserve

SCSEL: System clock select

00 = Internal 512 KHz RC oscillator output

Loading...

Loading...