380

7679H–CAN–08/08

AT90CAN32/64/128

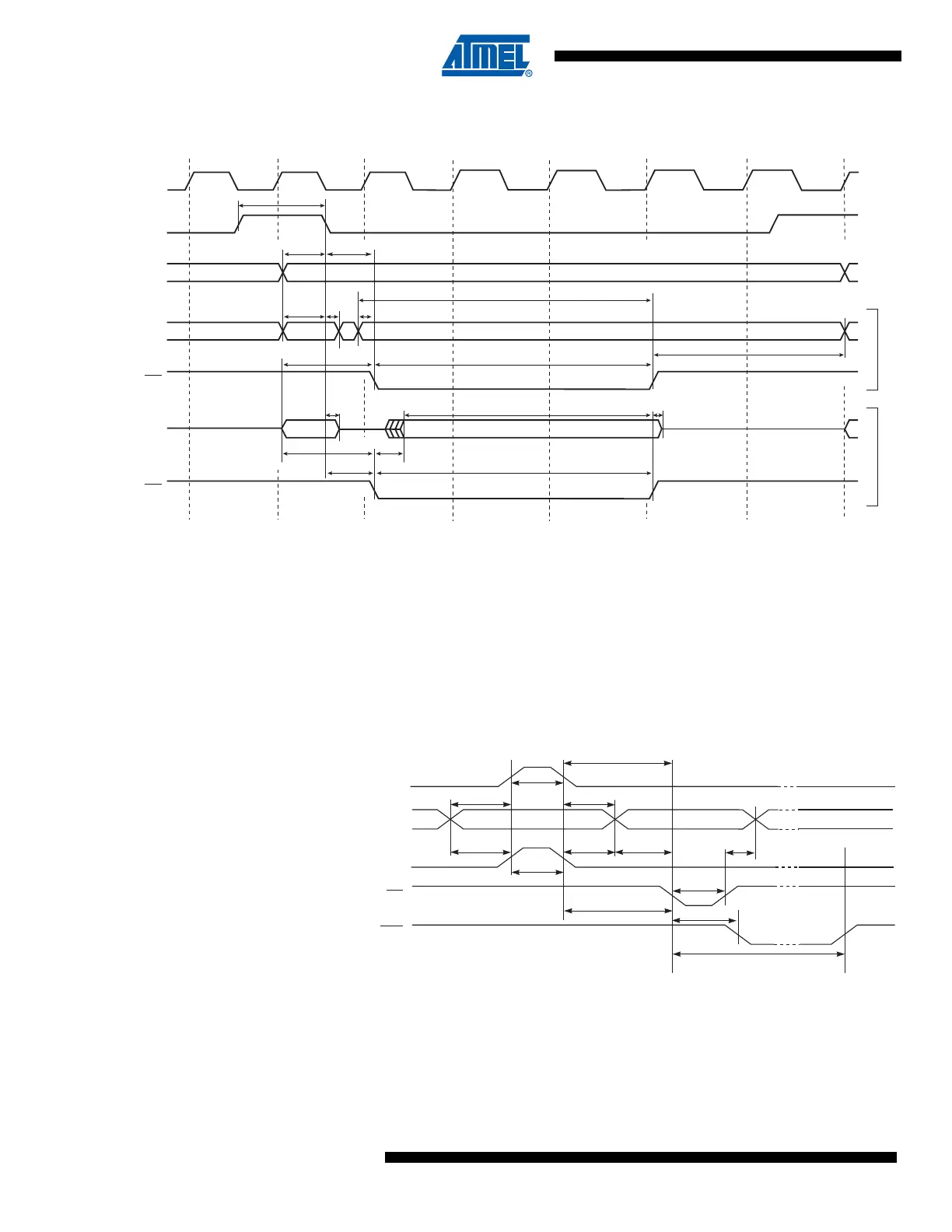

Figure 26-9. External Memory Timing (SRWn1 = 1, SRWn0 = 1)

(1)

Note: 1. The ALE pulse in the last period (T4-T7) is only present if the next instruction accesses the

RAM (internal or external).

26.10 Parallel Programming Characteristics

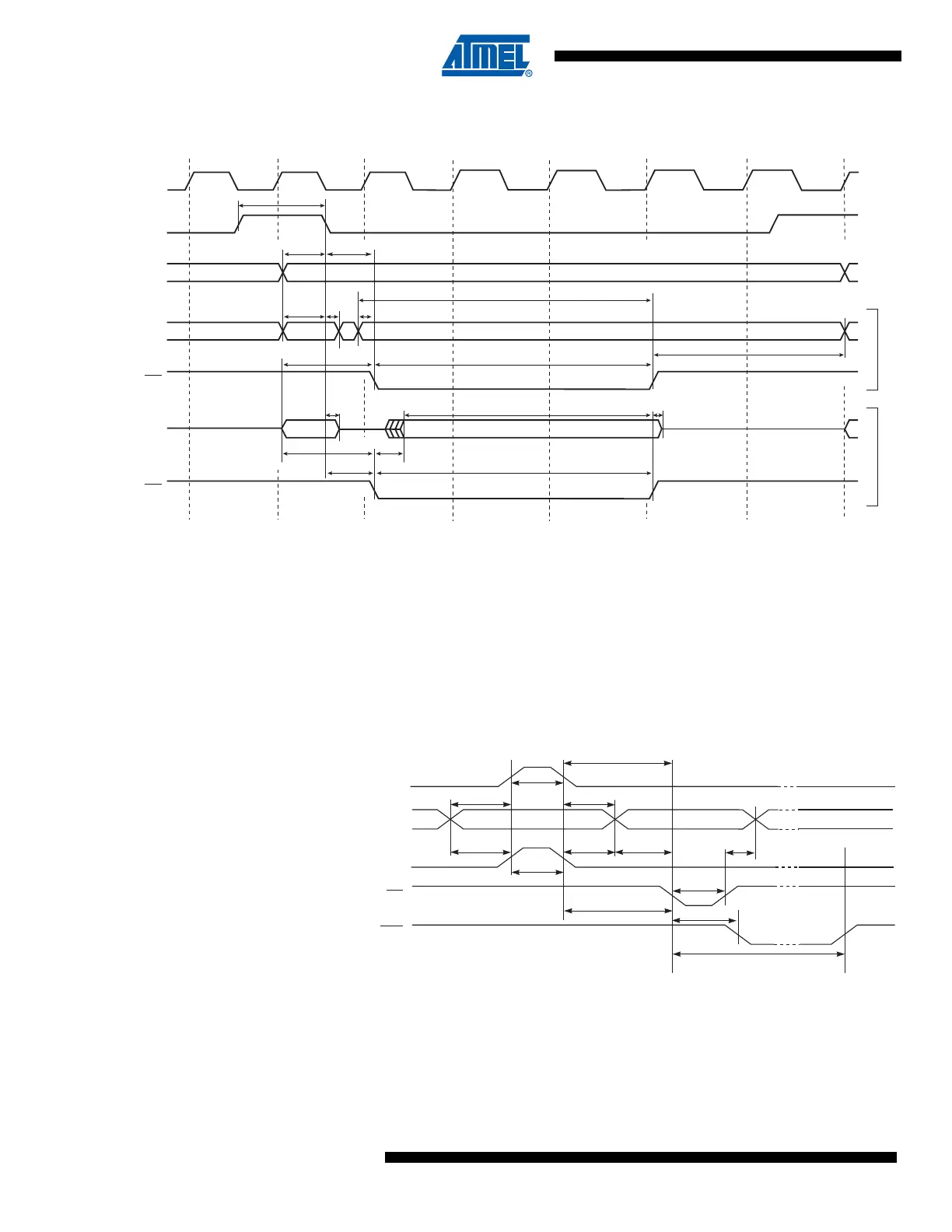

Figure 26-10. Parallel Programming Timing, Including some General Timing Requirements

ALE

T1 T2 T3

Write

Read

WR

T7

A15:8

Address

Prev. addr.

DA7:0

Address DataPrev. data XX

RD

DA7:0 (XMBK = 0)

Data

Address

System Clock (CLK

CPU

)

1

4

2

7

6

3a

3b

5

8 12

16

13

10

11

14

15

9

T4

T5

T6

Data & Contol

(DATA, XA0/1, BS1, BS2)

XTAL1

t

XHXL

t

WLWH

t

DVXH

t

XLDX

t

PLWL

t

WLRH

WR

RDY/BSY

PAGEL

t

PHPL

t

PLBX

t

BVPH

t

XLWL

t

WLBX

t

BVWL

WLRL

Loading...

Loading...