5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

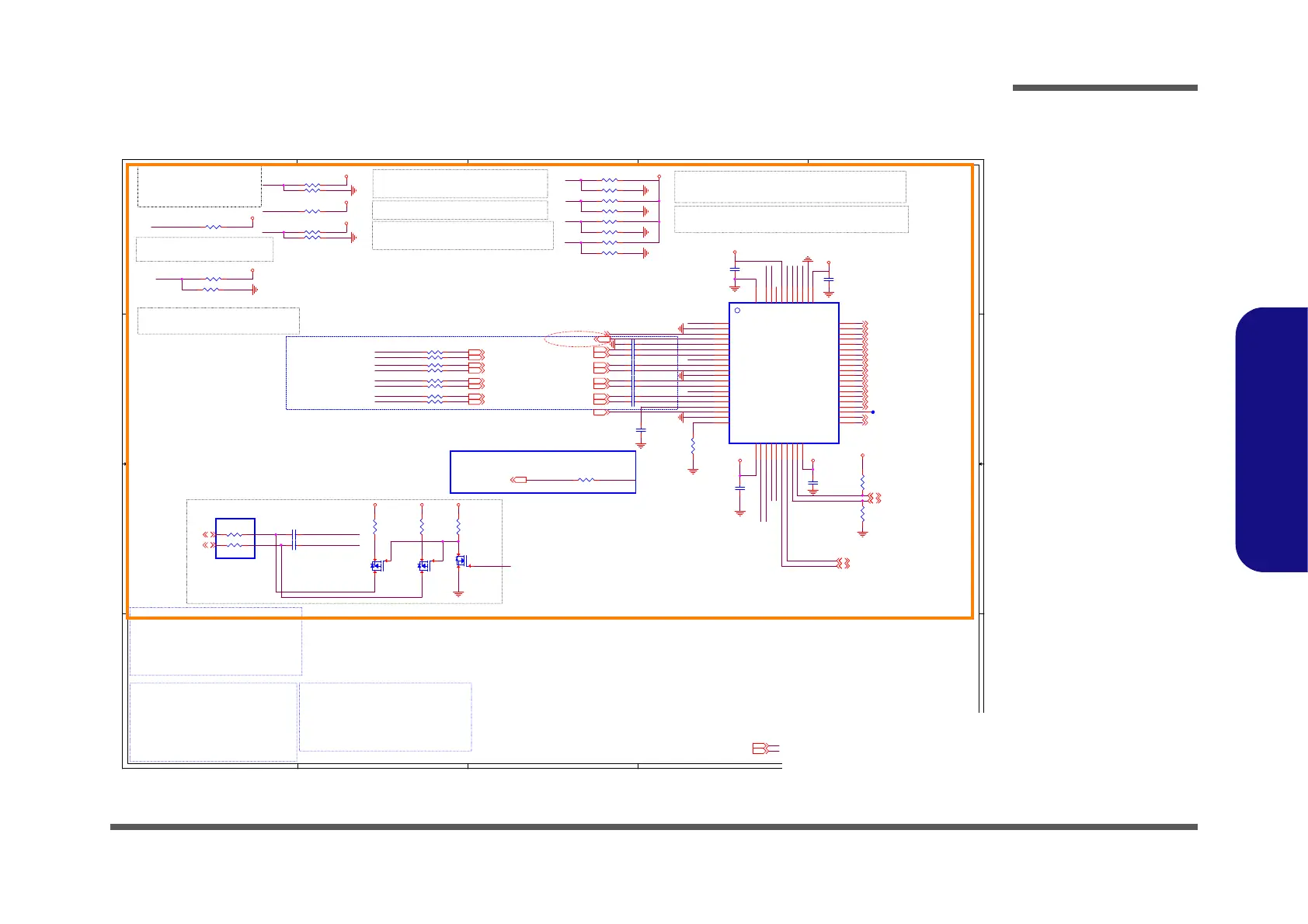

PD PIN:

L:Normal operation(default)

H:Chip power dow

DESIGN NOTE:CFG0

Configuration pin for automatic EQ and

Aux interception; Internal pull down at

150Kohm,3.3V I/O

L: default, automatic EQ enable and Aux interception enable

H: automatic EQ disable and AUX interception enable

M: automatic EQ disable and AUX interception

disable,no pre-emphasis, 600mVpp swing

DESIGN NOTE:CFG1

Configuration pin for auto test and input offset

cancellation,3.3V IO, internal pull up at 150K

H: default, auto test disable and input offset cancellation

enable

L: auto test enable and input offset cancellation enable

M: auto test disable and input offset cancellation disable

DESIGN NOTE:PEQ

Programmalbe input equalization levels;internal pull

down at 150k ,3.3v I/O

L: default, LEQ, compensate channel loss up to 12dB at

HBR2

H: HEQ, compensate channel loss up to 15dB at HBR2

M:LLEQ, compensate channel loss up to 5dB at HBR2

Auto test enable; Internal pull down at ~150K ohm, 3.3V I/O.

L: Auto test disable & input offset cancellation enable (default)

H: Auto test enable & input offset cancellation enable

M: Auto test disable & input offset cancellation disable

Automatic EQ disable; Internal pull down at ~150K ohm, 3.3V IO

L: Automatic EQ enable (default)

H: Automatic EQ disable

Programmable input equalization levels; Internal pull down at

~150K

㫉

, 3.3V I/O.

L: default, LEQ, compensate channel loss up to 11.5dB @ HBR2

H: HEQ, compensate channel loss up to 14.5dB @ HBR2

M: LLEQ, compensate channel loss up to 8.5dB @ HBR2

Port switching control or priority configuration;

Internal pull down at ~150K ohm, 3.3V I/O.

L: Port1 is selected or with higher priority (default)

H: Port2 is selected or with higher priority

Chip operational mode configuration;

Internal pull down at ~150K ohm, 3.3V I/O.

L: Control switching mode (default)

H: Automatic switching mode

3 Levels Input:

L: Low

H: High

M: VDD33/2, connect both

pull-up and pull-down resistors

AUX interception disable for Port y (y = 1, 2). Internal pull down at ~150K

㫉

, 9,2

L: AUX interception enable, driver configuration is set by link training (default)

H: AUX interception disable, driver output with fixed 800mV and 0dB

M: AUX interception disable, driver output with fixed 400mV and 0dB

Output swing adjustment for Port y (y = 1, 2). Internal pull down at ~150K

㫉

, 9,2

L: default

H: +20%

M: -16.7%

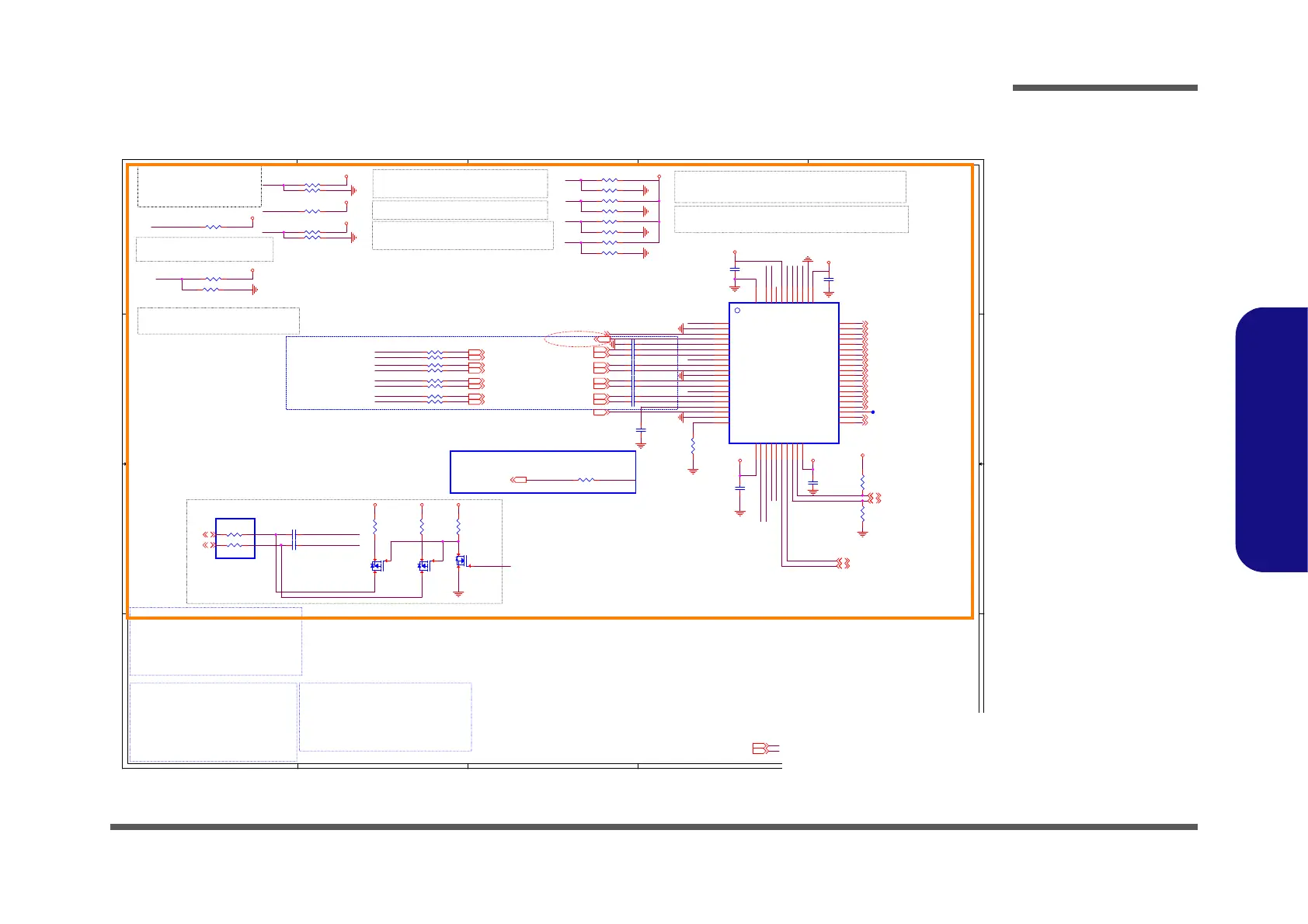

CO-LAY

TO DP

TO TBT

CO-LAY NV TO DP

ㇵᶲẞ

DEFAULT:LOW

Hybrid DDC/AUX

冯

R828

嶇

R839 CO-LAY

W/ TBT

ᶲ

ᶲᶲ

ᶲẞ

ẞẞ

ẞ

wey_0411

PC11

8338PD

PS8338B_PCH

8338PD

IN_D2p

PI1

PI0

PSCFG0

PC11

PC20

PC21

PC10

PSPEQ

3.3VS

IN_D1p

PSPEQ

3.3VS

IN_CA _D ET

PI0

PS8338B_SW

IN_D2n

IN_D3p

IN_D3n

PI1

PSCFG0

PS8338B_SW

MUX_AUXP

MUX_AUXN

IN_AUXp

IN_AUXn

PC10

PC21

PC20

IN_D0p

IN_D0n

IN_D1n

MDP_E#3

MDP_E3

MDP_E#2

MDP_E2

MDP_E#1

MDP_E1

MDP_E#0

MDP_E0

IN_AU Xn

GND

IN_CA _D ET

IN_AU Xp

MUX_AUXN

MUX_AUXP

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

NV3V3 NV3V3NV3V3

3.3VS[3,8,9,10,11,12,13,26,30,31,32,33,34,35,36,37,38,39,41,43,47,48,49,50,57,64]

NV3V3[11,12,13,14,26,52,53,61,62]

OUT1_AUXp_SCL [11]

OUT1_AUXn_SDA [11]

OUT1_D0p [11]

OUT1_D0n [11]

OUT1_D1p [11]

OUT1_D1n [11]

OUT1_D2p [11]

OUT1_D2n [11]

OUT1_D3p [11]

OUT1_CA_DET [11]

OUT1_HPD [11]

OUT2_D0p [42]

OUT2_D0n [42]

OUT2_D1p [42]

OUT2_D1n [42]

OUT2_D2p [42]

OUT2_D2n [42]

OUT2_D3p [42]

OUT2_D3n [42]

OUT2_HPD [42]

OUT1_D3n [11]

OUT2_AUXp_SCL [42]

OUT2_AUXn_SDA [42]

MDP_E_HPD[11,26,32]

MDP_E#0[25]

MDP_E0[25]

MDP_E#1[25]

MDP_E1[25]

MDP_E#2[25]

MDP_E2[25]

MDP_E#3[25]

MDP_E3[25]

MDP_E#0_R [11]

MDP_E0_R [11]

MDP_E1_R [11]

MDP_E#1_R [11]

MDP_E#2_R [11]

MDP_E2_R [11]

MDP_E#3_R [11]

MDP_E3_R [11]

PS8338B_PCH[34]

PS8338B_SW[31]

MDP_E_AUX_SCL[11,25]

MDP_E_AUX#_SDA[11,25]

IN_CA _D ET[11]

Title

Size Document Number Rev

Date: Sheet

of

6-71-PA700-D02A D02A

[46] TBT_DP(PS8338B)

A3

46 77Wednesday, July 05, 2017

Title

Size Document Number Rev

Date: Sheet

of

6-71-PA700-D02A D02A

[46] TBT_DP(PS8338B)

A3

46 77Wednesday, July 05, 2017

Title

Size Document Number Rev

Date: Sheet

of

6-71-PA700-D02A D02A

[46] TBT_DP(PS8338B)

A3

46 77Wednesday, July 05, 2017

R616

*4.7K_04

R260 0_04

R600 *4.7K_04

C893 0.1u_10V_X7R_04

R276 *4.7K_04

R818

*4.7K_04

R261 0_04

R621 *4.7K_04

R608 *4.7K_04

U39

PS8338B

PI1/SCL_CTL

1

I2C_CTL_EN

2

IN_HPD

3

IN_CA_DET

4

VDD33

5

IN_D0p

6

IN_D0n

7

PEQ

8

IN_D1p

9

IN_D1n

10

GND

11

IN_D2p

12

IN_D2n

13

PD

14

IN_D3p

15

IN_D3n

16

CEXT

17

SW

18

GND

19

REXT

20

VDD33

21

IN_DDC_SCL

22

IN_DDC_SDA

23

IN_AUXp

24

IN_AUXn

25

OUT1_AUXp_SCL

26

OUT1_AUXn_SDA

27

OUT2_AUXp_SCL

28

OUT2_AUXn_SDA

29

VDD33

30

OUT2_D3n

31

OUT2_D3p

32

OUT2_CA_DET

33

OUT2_D2n

34

OUT2_D2p

35

OUT2_D1n

36

OUT2_D1p

37

OUT2_HPD

38

OUT2_D0n

39

OUT2_D0p

40

OUT1_D3n

41

OUT1_D3p

42

OUT1_CA_DET

43

OUT1_D2n

44

OUT1_D2p

45

OUT1_D1n

46

OUT1_D1p

47

OUT1_HPD

48

OUT1_D0n

49

OUT1_D0p

50

VDD33

51

GND

52

PC21

53

PC20

54

PC11

55

PC10

56

VDD33

57

CFG1

58

CFG0

59

PI0/SDA_CTL

60

EPAD

61

Q65

AO3415

G

D S

C894 0.1u_10V_X7R_04

R258 0_04

C907

0.01u_50V_X7R_04

C500 0.1u_10V_X7R_04

Q66

2SK3018S3

G

DS

R259 0_04

R284

*4.7K_04

R280 *4.7K_04

C522 0.1u_10V_X7R_04

R256 0_04

C895 0.1u_10V_X7R_04

R620

100K_04

R821

4.7K_04

R257 0_04

R607

4.99K_1%_04

C898 0.1u_10V_X7R_04

R822

4.7K_04

R255 0_04

R613 *4.7K_04

C925

0.1u_10V_X7R_04

R830 0_04

TBT

Q44

AO3415

G

D S

R254 0_04

C892

2.2u_6.3V_X5R_04

R623

100K_04

C900 0.1u_10V_X7R_04

R246 *4.7K_04

R831 0_04

TBT

R823

4.7K_04

C899 0.1u_10V_X7R_04

R253 *4.7K_04

C897 0.1u_10V_X7R_04

C538 0.1u_10V_X7R_04

C896 0.1u_10V_X7R_04

C921

0.01u_50V_X7R_04

R603 *4.7K_04

R604 *4.7K_04

R245 *4.7K_04

C520

0.1u_10V_X7R_04

R272 *4.7K_04

R599 *0_04

R624

*4.7K_04

Loading...

Loading...