21

AVR-4802/AVC-A11SR

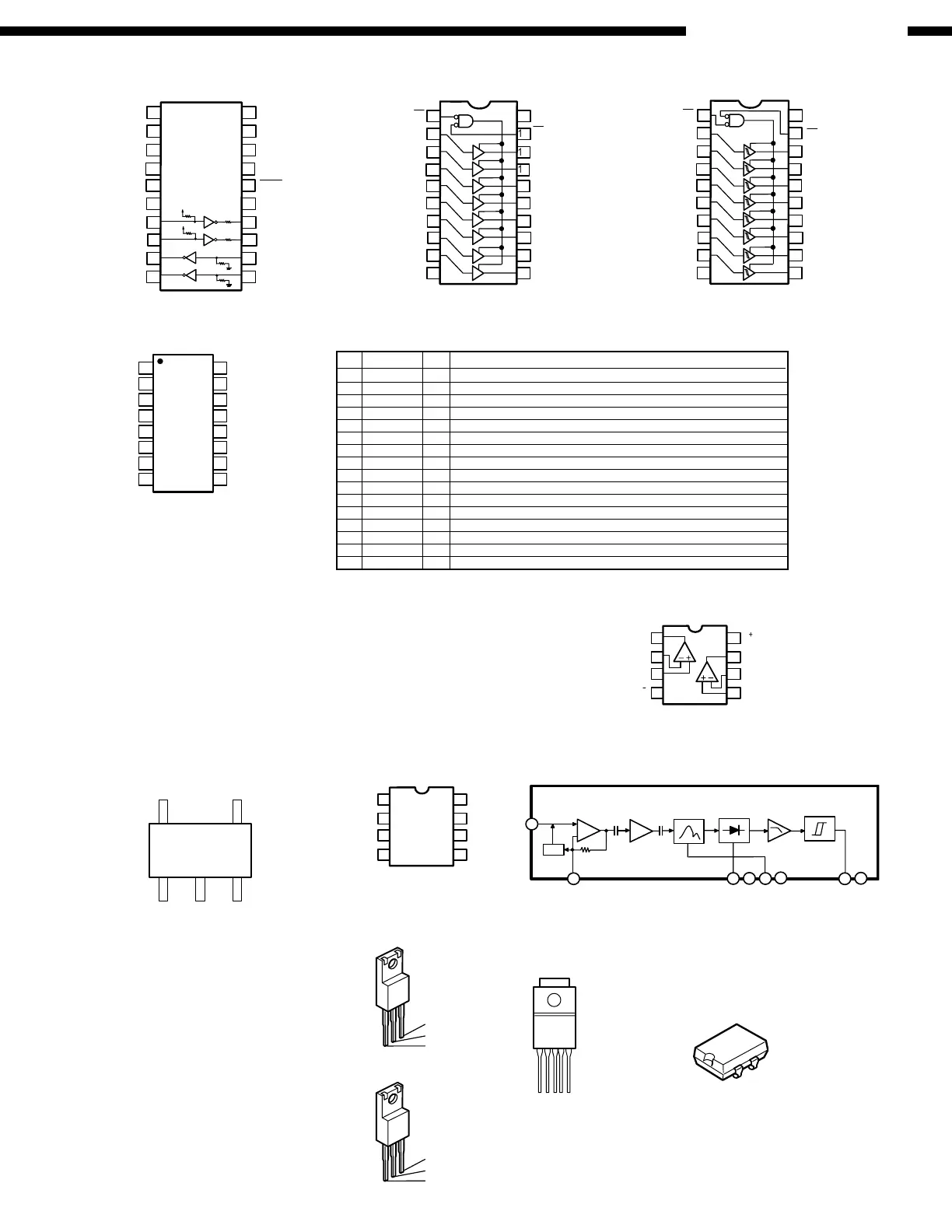

µPD4721GS-GJG (IC501)

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

G1

A1

A2

A3

A4

A5

A6

A7

A8

GND

Vcc

G2

Y1

Y2

Y3

Y4

Y5

Y6

Y7

Y8

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

G1

A1

A2

A3

A4

A5

A6

A7

A8

Vcc

G2

Y1

Y2

Y3

Y4

Y5

Y6

Y7

Y8

GND

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

5.5 k

Ω

5.5 k

Ω

300

Ω

300

Ω

C4+

GND

C4-

Vss

STBY

V

DD

C1+

Vcc

C1-

C5+

C5-

D

IN

1

D

IN

2

R

OUT

1

R

OUT

2

V

CHA

D

OUT

1

D

OUT

2

R

IN

1

R

IN

2

SN74LV541APW (IC518, 522, 803) SN74AHCT541PW (IC514)

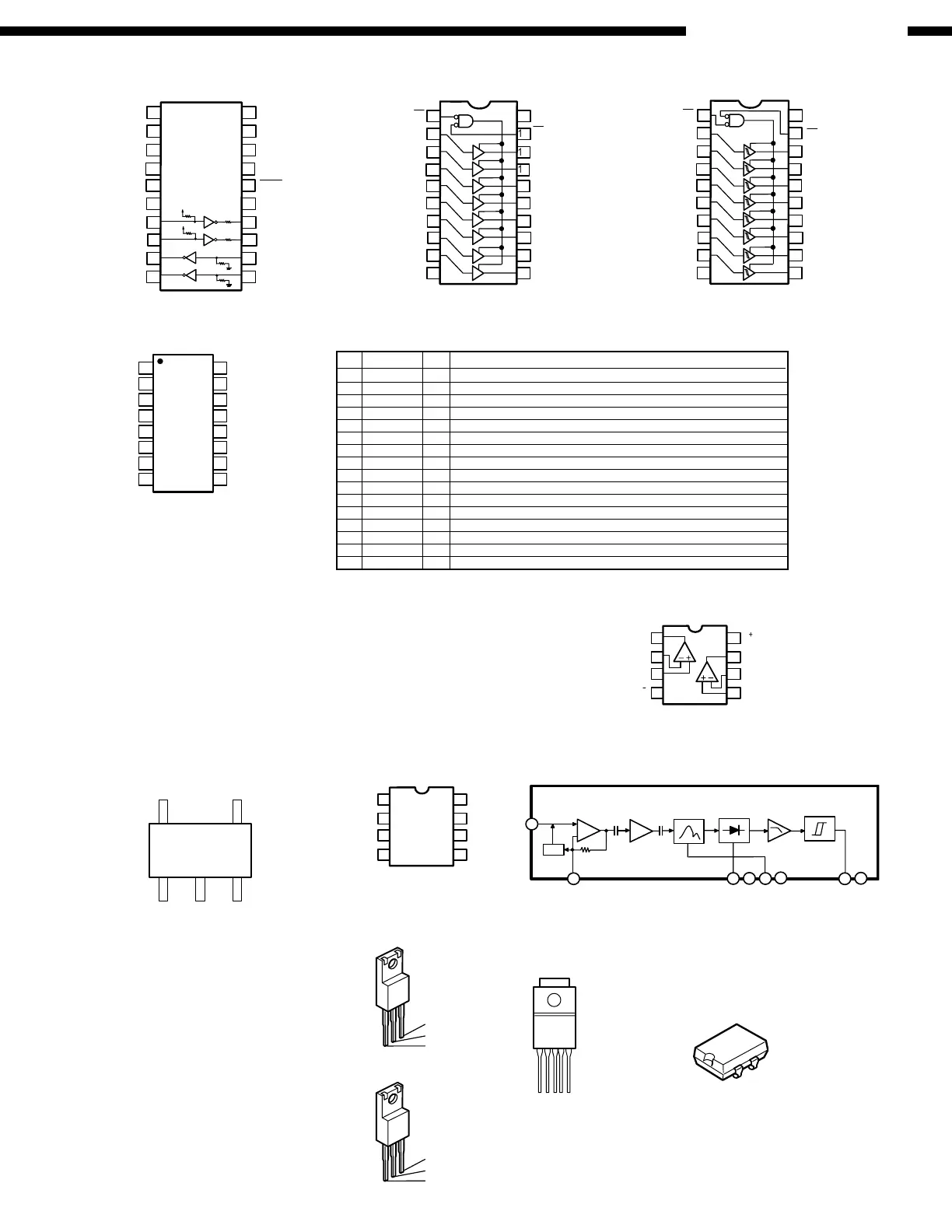

AK5353 (IC114)

AINR

AINL

VREF

VCOM

AGND

VA

VD

DGND

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

TST

TTL

DIF

PDN

SCLK

MCLK

LR C K

SDTO

BA4510F (IC115)

TK15420MTL (IC601~603, 606, 701~706, 713)

BA15218F (IC116, 118, 309~313)

NJM2068MD (IC101, 104~112, 117, 120, 201~204,

301, 302, 304, 306, 308, 402, 404, 471, 506~509)

NJM4556AD (IC502)

NJM5532MD (IC301, 303, 305, 307)

A OUTPUT

A INPUT

A +INPUT

V

B OUTPUT

V

B INPUT

B +INPUT

1

2

3

4

5

7

8

6

1

2

CXA1511M (IC502)

8

7

5

6

4

3

2

1

ABLC

+

H ead

Am p

Lim iter

Am p

BPF

BEF

D e te c to r &

C om parator

Integrator

H ysteresis

C om parator

C1 C2 GND fo NC OUTVcc

IN

ABLC

BA033T (IC526, 527)

KIA7806API (IC203)

KIA7812API (IC701)

KIA7820API (IC704, 709, 710)

KIA7805API (IC309, 310, 702, 705)

KIA7815API (IC707)

Output

GND

Input

4

1

2

3

1. OE or ST

2. GND

3. OUT

4. V

DD

HG-8002JA33MHZPCCX

(X'tal Oscillator)

(IC510)

SN74AHC1G04DBV (IC109)

IN

C1

C2

GND

OUT

Vcc

NC

fo

1

2

3

4

5

7

8

6

1

23

FRONT

VIEW

45

1. CTL

2. Vcc

3. GND

4. OUT

5. N.C.

BA08ST (IC205)

TOP VIEW

13

54

KIA7905PI (IC703, 706)

KIA7915PI (IC708)

Output

Input

GND

Terminal Function

No. Name I/O Function

1 AINR I Rch analog input pin

2 AINL I Lch analog input pin

3 VREF O Ref. V out pin

4 VCOM O Common V out pin

5 AGND Analog GND pin

6VA Analog power pin, +2.7~+5.5

7VD Digital power pin, +2.7~+5.5V

8 DGND Digital GND pin

9 SDTO O Serial data out pin, 2’s complement, MSB first out, at power down: L

10 LRCK I L/Rch clock pin

11 MCLK I Master clock input pin

12 SCLK I Serial data clock input pin, A/D data out at SCLK falling edge

13 PDN I Power down pin, L: Power down mode

14 DIF I Serial interface format pin (L: Firward, H: I

2

S)

15 TTL I Digital input level select pin, L: CMOS level, H: TTL level

16 TST I Test pin (internal pull-down)

Loading...

Loading...