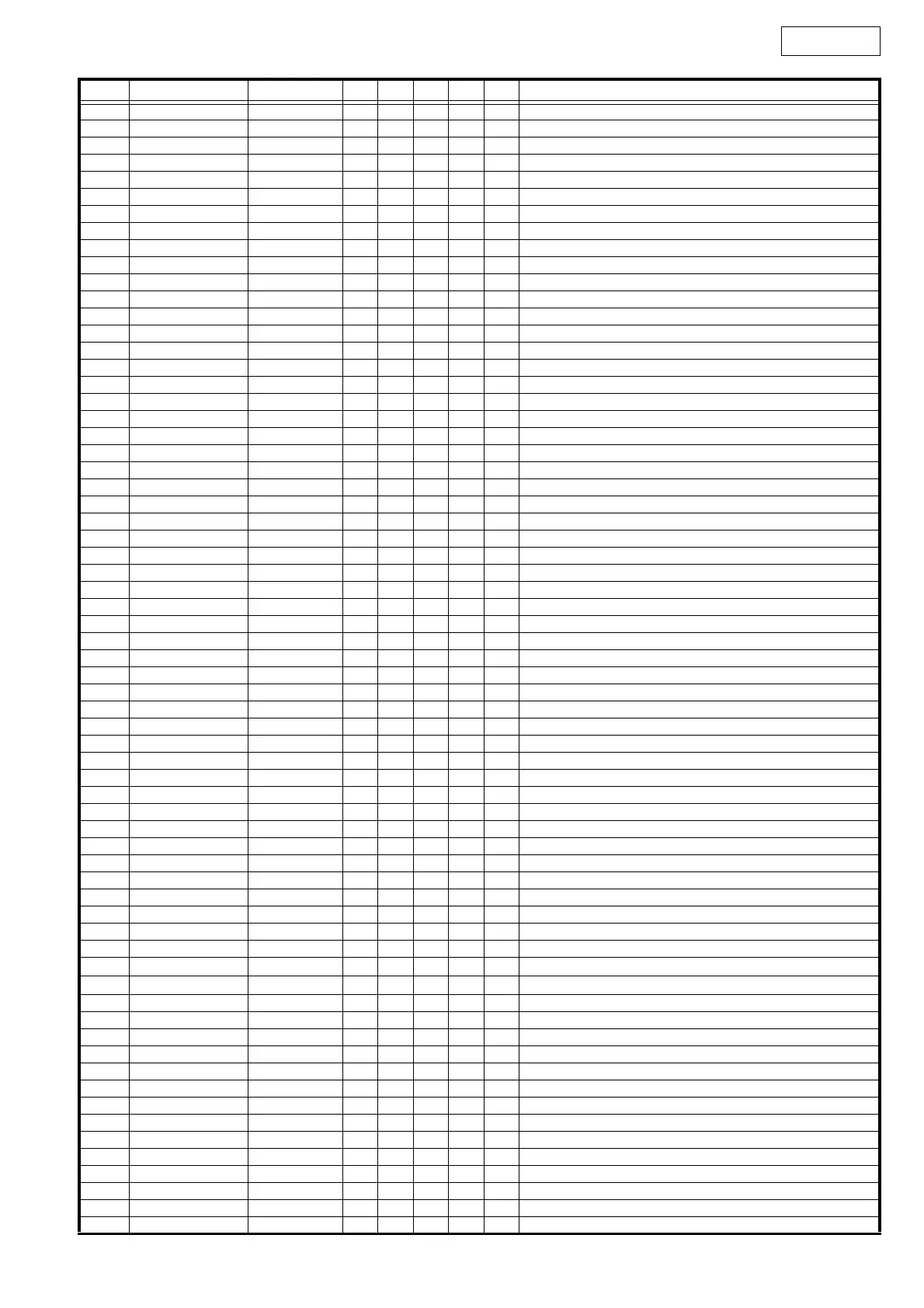

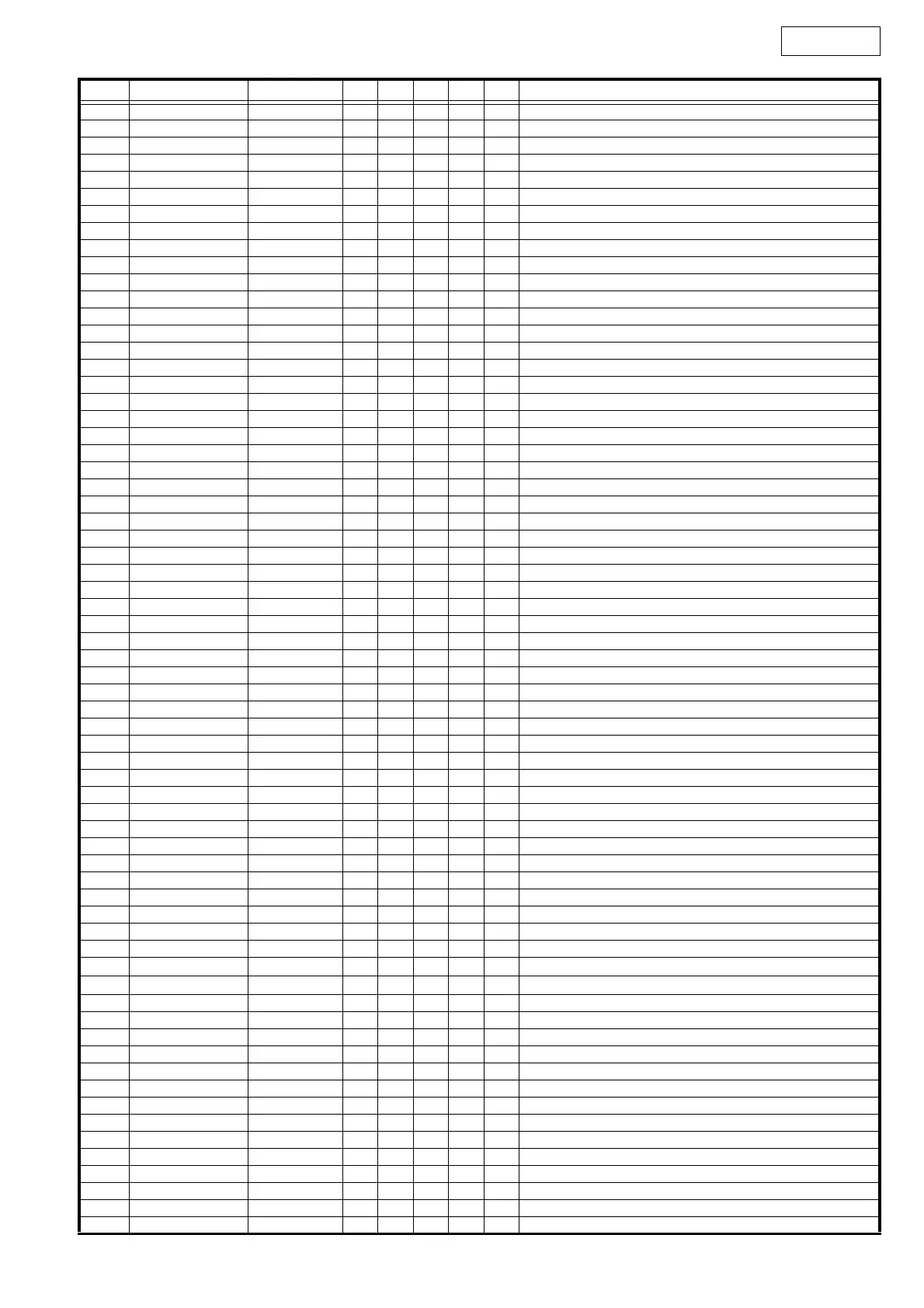

12

DN-D4500

34PC5,NMI_ NMI I----Connect to Power

35RST_ RST_ I----ucom reset

36 PC0 _MUTE O Pd L Mute signal (L: Mute)

37 P76,TM13IOA LOAD2 O - Tray Loading / Eject signal (PWM output) (Driver2)

38 P60,IRQ0 FSYNC1 I iPu X2: Clock for playback interrupt input / X1: LRCK (MP3)

39 P61,IRQ1 BLKCK1 I iPu Sub cord clock interrupt (Servo DSP1)

40 P62,IRQ2,TM10IOA FSYNC2 I iPu X2: Clock for playback interrupt input / X1: LRCK (MP3)

41 P63,IRQ3,TM10IOB DQSY1 I iPu CD-TEXT DQSY interrupt (Servo DSP1)

42 P64,IRQ4 O iPu

43 P65,IRQ5,TM12IOA O iPu

44 P66,IRQ6 BLKCK2 I iPu Sub cord clock interrupt (Servo DSP2)

45 P67,IRQ7 DQSY2 I iPu CD-TEXT DQSY interrupt (Servo DSP2)

46 P70,TM13IOB EJECTSW2 I iPu CD2 Eject SW

47 P71 LED2 O Pu L Tray LED (CD2)

48 PD2,DMAACK0_ CHGOFT1 O Pu L H Off-track signal (CD1)

49 PD3,TM3IO DAC1MLD O iPu H Hiz PCM1748_1 Control Latch output signal

50VDD VDD -----Power (+3.3V)

51 P77,TM14IOA LOAD1 O - Hiz Tray Loading / Eject signal (PWM output) (Driver1)

52 P72,TM14IOB MON2_M1 I iPu Servo DSP1 monitor signal 2

53 P73 _LSI_RESET1 O Pd L L Servo DSP1 / 2 reset signal

54 P74 MLD1 O iPu H Hiz Servo DSP1 latch output signal

55 P75,TM12IOB _LSI_RESET2 O Pd L L Not used

56 PA0,SBI0 STAT1 I iPu Servo DSP1 interface receive (clock sync)

57 PA1,SBO0 MDATA1 O Servo DSP1 interface send (clock sync)

58 PA2,SBT0 MCLK1 O Servo DSP1 interface clock (clock sync)

59 PA3,SBI1 STAT2 I iPu Servo DSP2 interface receive (clock sync)

60 PA4,SBO1 MDATA2 O Servo DSP2 interface send (clock sync)

61 PA5,SBT1 MCLK2 O Servo DSP2 interface clock (clock sync)

62 PB0,SBI2 DSPTXD(RXD) I Pu H DSP interface receive (UART)

63 PB1,SBO2 DSPRXD(TXD) O Pu H DSP interface send (UART)

64 PB2,SBT2 O iPu L

65 PB3,SBI3 RXDRC I Pu RCD45 interface receive (UART)

66 PB4,SBO3 TXDRC O Pu RCD45 interface send (UART)

67 PB5,SBT3 O iPu L

68VDD VDD -----Power (+3.3V)

69VSS VSS -----GND

70AVSS AVSS -----Analog ref. GND for A/D conversion, GND

71Vref- Vref- -----Analog ref. V for A/D conversion, GND

72 P80 OPENSW1 I Pu CD1 Tray open SW L:ON

73 P81 CLOSESW1 I Pu CD1 Tray close SW L:ON

74 P82 INSW1 I Pu CD1 Inner SW L:ON

75 P83 FPLAY1 I Pu Fader PLAY1 input

76 P84 FCUE1 I Pu Fader CUE1 input

77 P85 FPLAY2 I Pu Fader PLAY2 input

78 P86,AD06 FCUE2 I Pu Fader CUE2 input

79 P87,AD07 MON2_M2 I iPu Servo DSP2 monitor signal 2

80 PD4 MLD2 O iPu Servo DSP2 latch output signal

81 PD5 CHGOFT2 O Pu Off track signal (CD2)

82 P90 DAC2MLD O iPu PCM1748_2 Control Latch output signal

83 P91 O iPu Reserved

84 P92 DEBUG1 I iPu

DSP → SYSTEM Reserved (CD1)

85 P93 DEBUG2 I iPu

DSP → SYSTEM Reserved (CD2)

86Vref+ Vref+ -----Analog ref. V for A/D conversion, +3.3V

87AVDD AVDD -----Power (+3.3V)

88 P94 LDEND1 I iPu Loading end (CD1)

89 P95 DSPIF1 O iPu Flag1 for DSP

90 P96,DAC2 DSPIF0 O iPu Flag0 for DSP

91 P97,DAC3 _DSPRES O Pd DSP reset signal L: RESET

92 PC6,BREQ_ _BREQ I Pu Bus request signal

93 PC7,BRACK_ _BRACK O Pu Bus request accept signal

94 WEL_ WE_ O - Pu - H Ext. memory write enable (Lower 8 bit)

95 P51 _BOOT O Pu DSP boot start signal L: START

96 RE_ RE_ O - Pu - H Ext. memory read enable

97CS2_ CS2_ O----Ext. memory chip select 2 (Not used)

98VDD VDD -----Power (+3.3V)

99VSS VSS -----GND

Pin No. Pin Name Simbol I/O DET Ext Ini Res Function

Loading...

Loading...