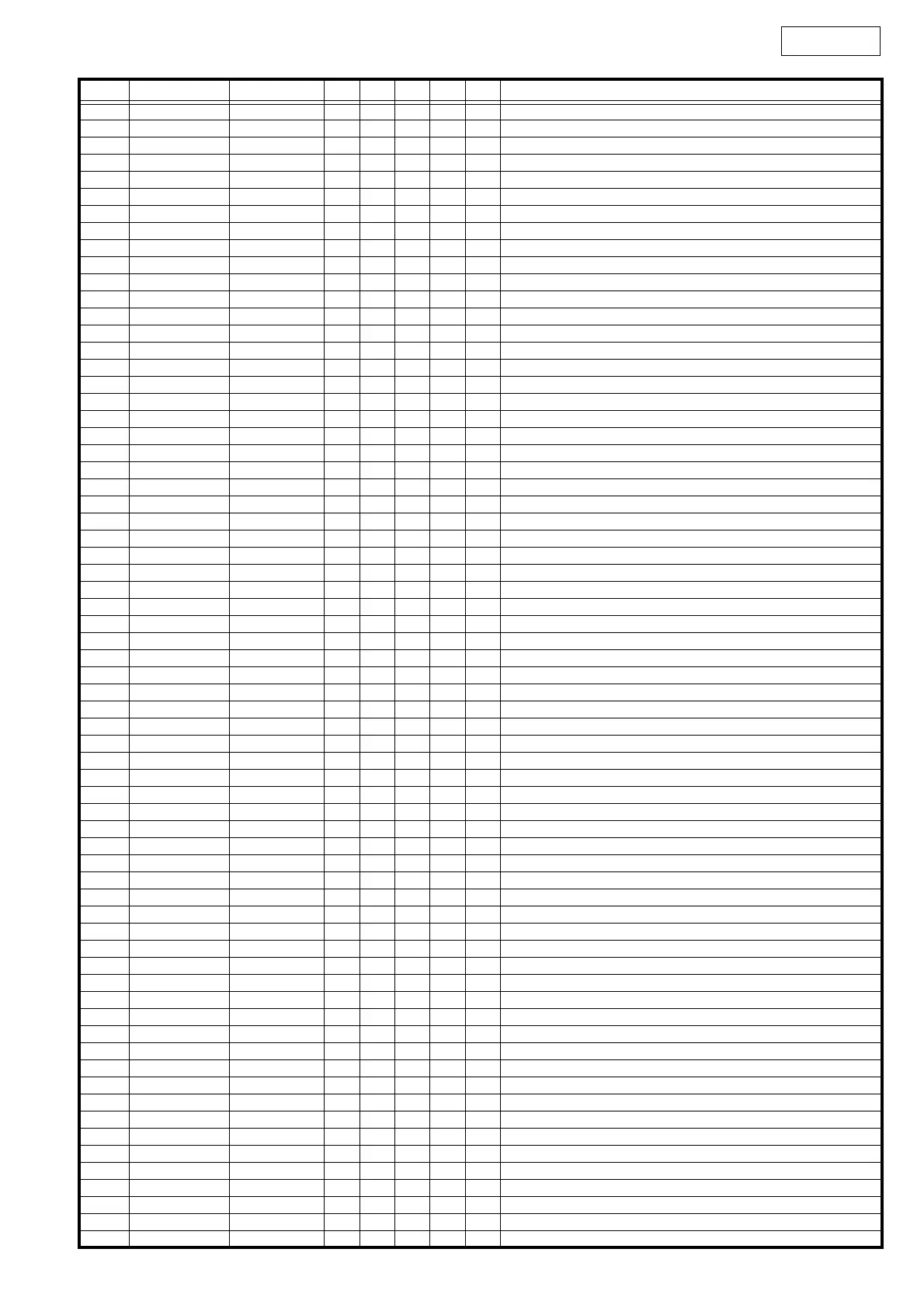

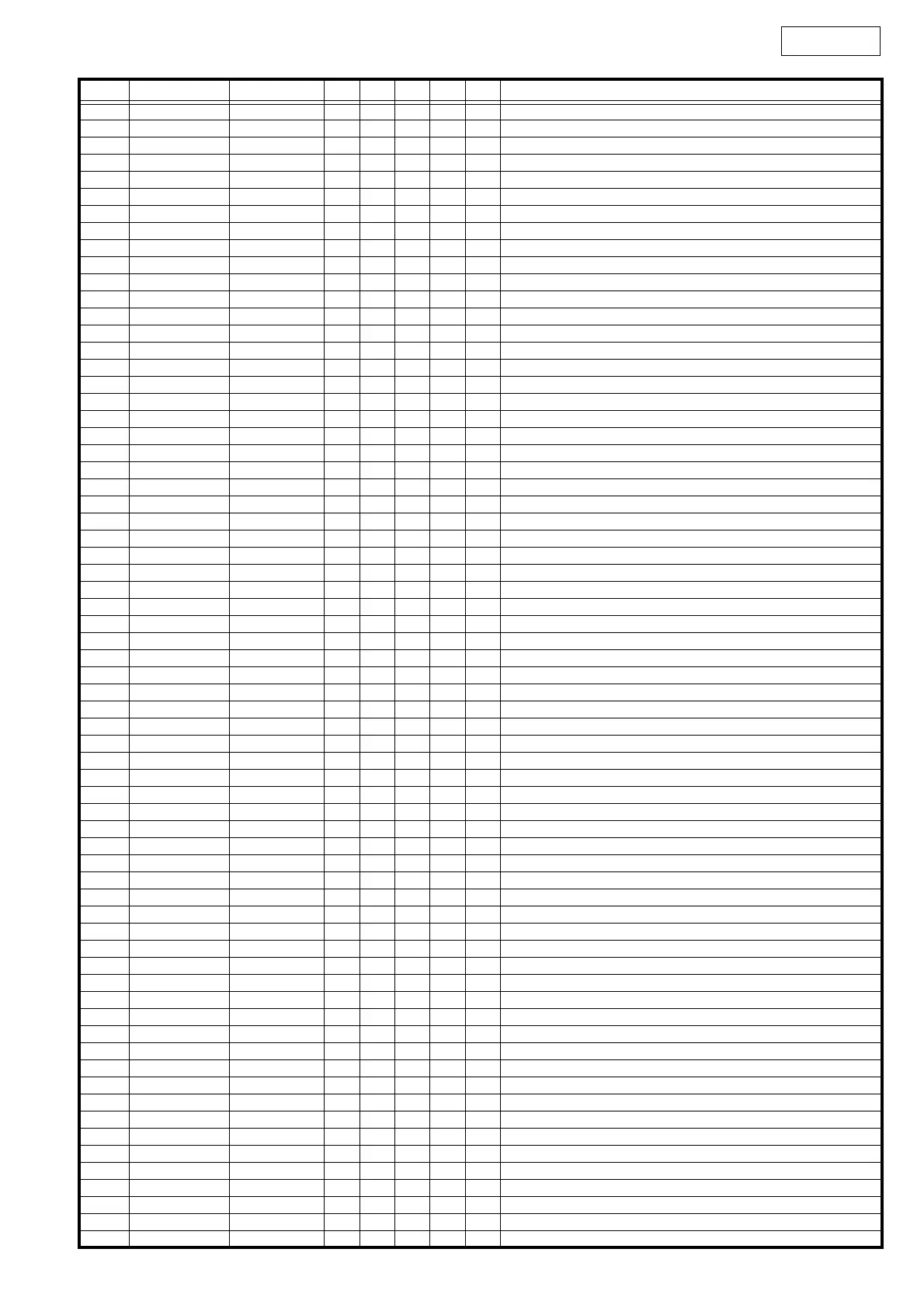

15

DN-D4500

45VDDEXT VDDEXT I----I/O power supply (+3.3V)

46 PF5 LDEND2 O - - L - Loading end (CD2)

47 PF4 DSPF1 O - - L - Flag1 for DSP

48 PF3 LDEND1 O - - L - Loading end (CD1)

49 PF2 DSPF0 O - - L - Flag0 for DSP

50 PF1 FSYNC1 O - - L - X2: Clock for playback interrupt input / X1: LRCK (MP3)

51 PF0 BTEND O - Pd L L Programmable flag 0, All end : H

52VDDINT VDDINT I----Core power supply (+1.2V)

53 SCK O - - L - Master slave clock

54 MISO O - - L - Master in slave out

55 MOSI O - - L - Master out slave in

56GND GND -----GND

57VDDEXT VDDEXT I----I/O power supply (+3.3V)

58 DT1SEC DDATA2 O - - L - Digital out data send 0 (serial port OUT 1) (CD2)

59DT1PRI DDATA1 O----Digital out data send 0 (serial port OUT 1) (CD1)

60 TFS1 DLRCK I - IPu - H Digital out send frame sync (LRCK) signal (serial port OUT 1)

61TSCLK1 DBCLK I----Digital out send frame sync (BCK) signal (serial port OUT 1)

62 DR1SEC SRDATA2 I - - L L Playback data receive 1 (serial port IN 1) (CD2)

63 DR1PRI LRCK2 I - - L L Receive frame sync (LRCK) signal (serial port IN 1) (CD2)

64 RFS1 BCLK2 I - IPu L - Receive frame sync (BCK) signal (serial port IN 1) (CD2)

65 RSCLK1 O - - L - Receive frame sync (BCK) signal (serial port IN 1)

66VDDINT VDDINT I----Core power supply (+1.2V)

67 DT0SEC ADATA2 O - - L - Analog playback data send 0 (serial port OUT 0) (CD2)

68DT0PRI ADATA1 O----Analog playback data send 0 (serial port OUT 0) (CD1)

69 TFS0 ALRCK I - IPu - H Analog playback send frame sync (LRCK) signal (serial port OUT 0)

70GND GND -----GND

71VDDEXT VDDEXT I----I/O power supply (+3.3V)

72TSCLK0 ABCLK I----Analog playback send frame sync (BCK) signal (serial port OUT 0)

73 DR0SEC I - - L L Playback data receive 1

74DR0PRI SRDATA1 I----Playback data receive 0 (serial port IN 0) (CD1)

75RFS0 LRCK1 O----Receive frame sync (LRCK) signal (serial port IN 0) (CD1)

76 RSCLK0 BCLK1 I - IPu - H Receive frame sync (BCK) signal (serial port IN 0) (CD1)

77 TMR2 O - - L - Timer 2

78 TMR1 O - - L - Timer 1

79 TMR0 O - - L - Timer 0

80VDDINT VDDINT I----Core power supply (+1.2V)

81 TX TX O - - H - UART send

82 RX RX I - Pu - H UART receive

83_EMU _EMU O----Emulation status

84 _TRST _TRST I - Pd - L Test reset (JTAG)

85 TMS TMS I - Pu - H Test mode select (JTAG)

86 TDI TDI I - Pu - H Test data input (JTAG)

87TD0 TD0 O----Test data output (JTAG)

88GND GND -----GND

89GND GND -----GND

90GND GND -----GND

91GND GND -----GND

92GND GND -----GND

93VDDEXT VDDEXT I----I/O power supply (+3.3V)

94 TCK TCK I - Pu - H Test clock (JTAG)

95BMODE1 BMODE1 I----Boot mode strap 1

96BMODE0 BMODE0 I----Boot mode strap 0

97GND GND -----GND

98DATA15 D15 I/O----Ext. bus data 15

99DATA14 D14 I/O----Ext. bus data 14

100DATA13 D13 I/O----Ext. bus data 13

101DATA12 D12 I/O----Ext. bus data 12

102DATA11 D11 I/O----Ext. bus data 11

103DATA10 D10 I/O----Ext. bus data 10

104DATA9 D9 I/O----Ext. bus data 9

105DATA8 D8 I/O----Ext. bus data 8

106GND GND -----GND

107VDDEXT VDDEXT I----I/O power supply (+3.3V)

108DATA7 D7 I/O----Ext. bus data 7

109DATA6 D6 I/O----Ext. bus data 6

110DATA5 D5 I/O----Ext. bus data 5

111VDDINT VDDINT I----Core power supply (+1.2V)

Pin No. Pin Name Symbol I/O DET Ext Ini Res Function

Loading...

Loading...