Remote Control

Page 22

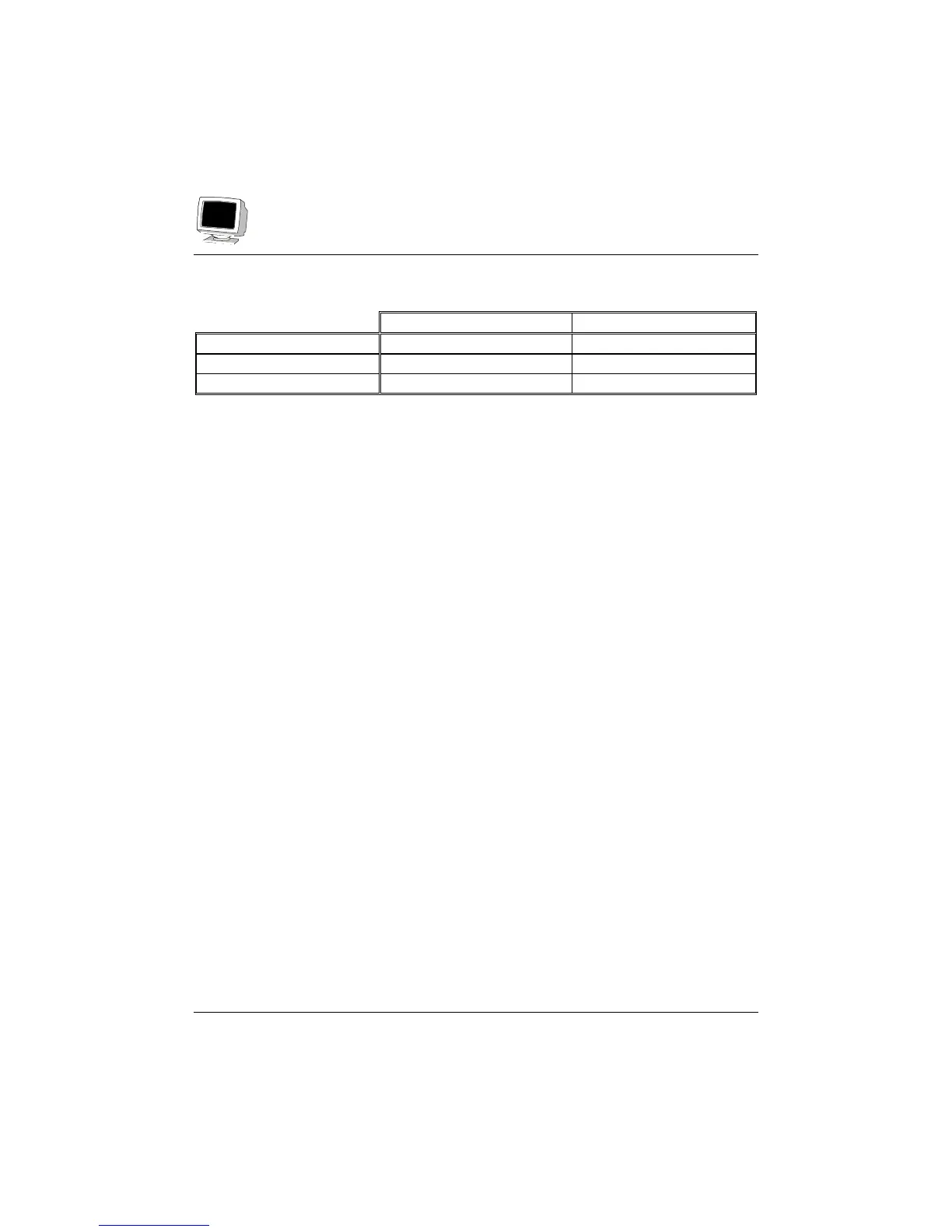

For both registers there are three basic commands: one to read the register, one to set the

enabling bits, and one to read the enabling bits.

Status Byte Register Event Status Register

Read Register *STB? *ESR?

Set Enabling Bits *SRE <NRf> *ESE <NRf>

Read Enabling Bits *SRE? *ESE?

Where <NRf> is the new value of the register.

4.5.1 Status Byte Register (STB)

The bits of this register are mapped as follows :

bit 4: MAV (Message Available Bit)

Indicates that the Output Queue is not empty. If MAV goes high and is

enabled then MSS goes high.

bit 5: ESB (Event Status Bit)

It indicates that at least one bit of the Event Status Register is non zero and

enabled. If ESB goes high and is enabled then MSS goes high.

bit 6: MSS/RQS (Master Summary Status/Request Service)

MSS is raised when either MAV or ESB are raised and enabled. When the

status of MSS changes, the whole Status Byte Register is copied into the Status

Byte of the GPIB controller, where bit 6 is called RQS. When RQS goes high

so does the SRQ line, and in response to an IEEE 488.1 Serial Poll command,

both are cleared.

RQS and SRQ are defined by the IEEE 488.1 standard and are hardware

related. MSS summarizes all the status bits of the DLS 50, as defined by the

IEEE 488.2 standard.

bits 7, 3, 2, 1,and 0 are not used by the DLS 50.

Loading...

Loading...