7.3 Processor Unit: RPU-013

7-32

7.3.3 SPU board (03P9337)

This board can be used commonly for FAR-2xx7 series.

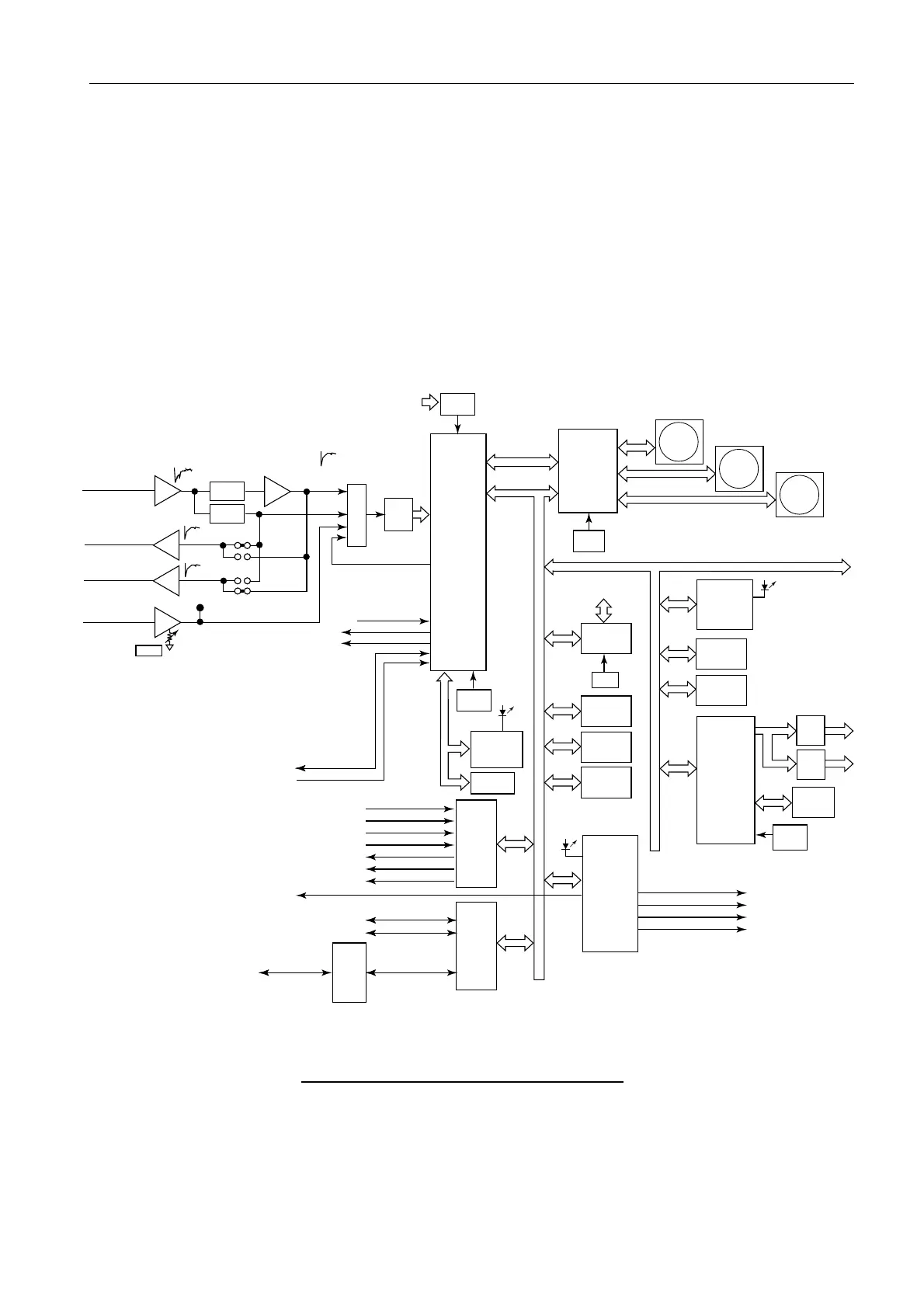

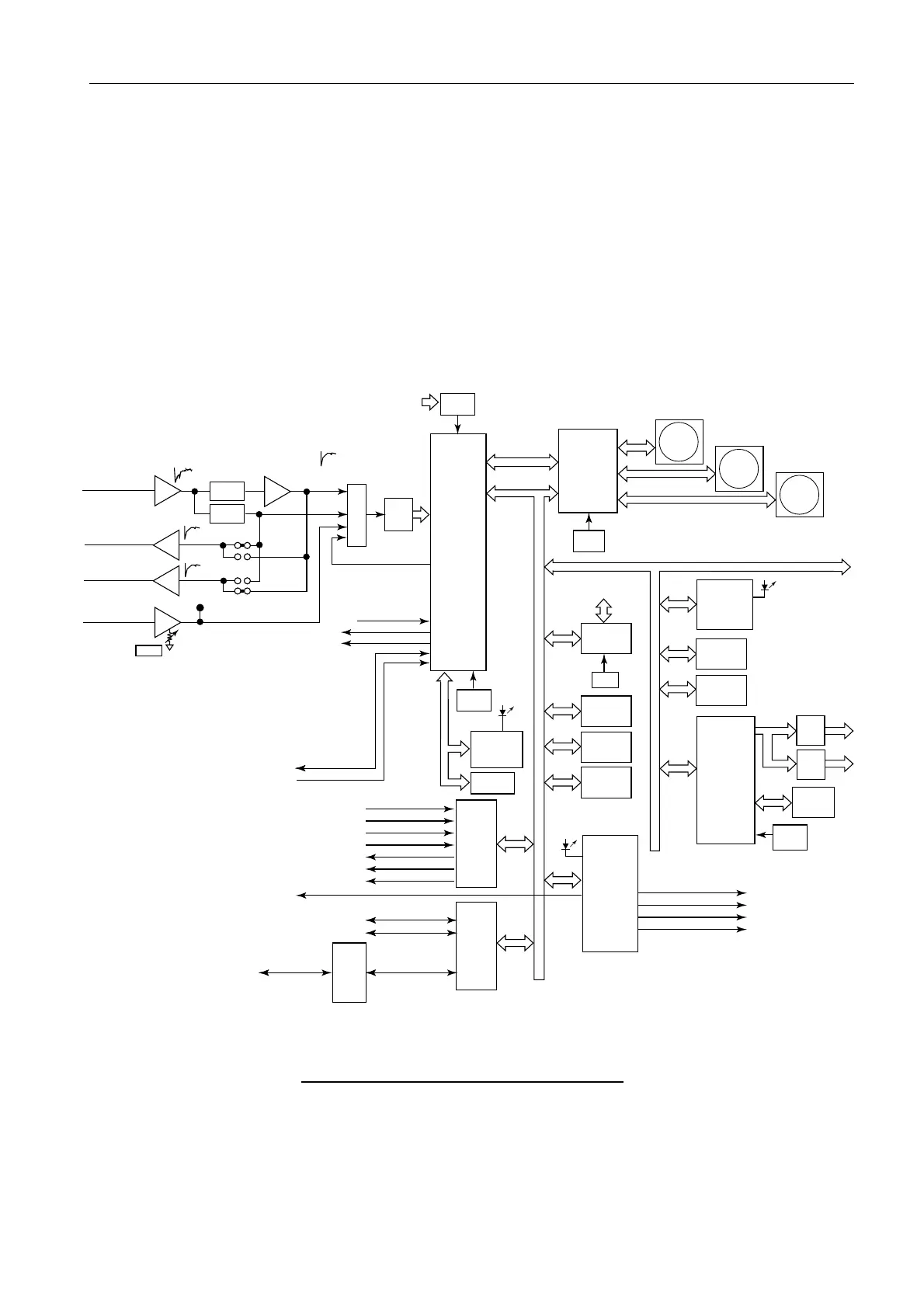

1. Block diagram

The SPU board performs picture, LAN, video amplifier, ARPA and video plotter

processing in addition to the control over the whole radar. The CPU is comprised of

three components of Main CPU, ARPA CPU, DRW CPU.

Fig. 7.3.5 Block diagram of the SPU board

IF-VIDEO-MIX

OP-VIDEO IN

OP-VIDEO IN

TEST Echo

+5V/+3.3V/+12V/-12V

TX ON

(From MAIN CPU)

MON MOTOR

(From PWRpcb))

FULL-LOG

OP1-VIDEO OUT

FULL-LOG

SEMI-LOG

OP2-VIDEO OUT

SEMI-LOG

U76

A/D

U19

DRW CPU

U28

SDRAM

U5

DVI

U4

DVI

U56

SDRAM

U38

A/D

U3

Display

MEMORY

U2

Echo

MEMORY

U1

Trail

MEMORY

U48

Flash ROM

(Program)

U47

DATA ROM

(Backup)

U22

SDRAM

U21

MAIN CPU

U15

FROM

U6

FROM

U46

SPU

FPGA

U12

Echo

FPGA

U13

DRW FPGA

U16

DRW

SDRAM

U64

FROM

U78

To Display

LAN

To NET-100

U78

U87

U83(Selecter)

U85

U74

ARPA CPU

U27

SPU

Controller

U9

SDRAM

30M

LPF

30M

HPF

JP3

TP58

R401

JP4

JP6

JP5

U86:Video DET

U85

8bit

MONOTOR

DATA/ADD

DATA/ADD

DATA/ADD BUS

CR4

CR6

CR8

Echo Data

U52

Serial I/O

RSV1 TD

RSV2 TD

ARPA TD

NAV RD

AIS RD

AIS TD

GYRO RD

LOG RD

EXT ALM 1-4

EXT ALM ACK

ANT ON

GC LED/UP/DOWN/HOLD

U73

Serial I/O

RS232C TTL Tx/RxRS232C Tx/Rx

KEY TD/RD

TRK TD/RD

U39

RS232C Driver

RF Tx/Rx

GYRO CLK/Data

OP HD/BP/TRIG

OP-2 HD/BP/TRIG

OP-1 HD/BP/TRIG

etc.

S1

Loading...

Loading...